# 釋放開源評估平台的潛力 製作超音波發射子系統的原型

本文討論開發先進超音波設備所面臨的挑戰,内容談及如何利用現有評估平台降低系統開發成本,同時縮短超音波系統發射模組的特性測試時間。本文並介紹如何同步多個通道的分步過程,這是波束控制的一個關鍵概念,也是醫學成像所特有的概念。

■作者: Sunshine Grace Cabatan / ADI 主管工程師 Melissa Lorenz Lacanlale / ADI 產品工程師

## 引言

在任何新技術開發過程中,在將新型號或下一代超音波設備商業化之前,製造商都會經歷硬體開發和測試以及系統整合和驗證等階段。開發高通道數成像超音波子系統往往預計需耗費多年的心力,此外,在對系統考量因素知之甚少的情況下,貿然開始波束引導或發射子系統的硬體原型製作可能會導致硬體原型需要多次修改,進而產生高昂的成本。現在,開發人員可以使用一個完整系統(原型板和開源軟體)來類比超音波設備子系統的操作,進而降低超音波設備製造商的開發成本,並加速上市時間。

## 基於 Arduino 的 TxDAC 評估板和開源 Mbed 軟體

AD9106-ARDZ-EBZ 評估平台相容基於 Arm 且支援 Mbed 的電路板 (如 SDP-K1),並 且可以連接到 Arduino Uno 接頭。該評估設定 只能由 USB 供電,無需高頻波形產生器來提供 時脈輸入。該評估板默認使用板載 156.25 MHz 晶振作為時脈源,但提供了外部時脈選項。 DAC 輸出可以透過變壓器耦合,或使用板載

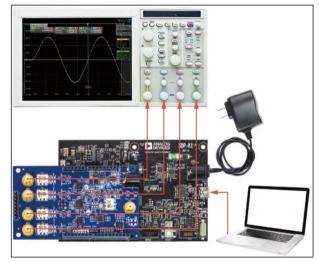

圖 1:支援 Mbed 的 AD9106 評估平台。

放大器進行評估,這是唯一需要 7 VDC 至 12 VDC 30 W AC-DC 轉接器的情况。參見圖 1。

除硬體之外,評估板網頁上還提供了示例開原始程式碼,可用於開發目標應用韌體的起點。評估板和示例原始程式碼可以根據需要加以客製,以便與其他 Mbed 平台配合使用。新的評估系統可以輕鬆整合到現有系統中,因而簡化了原型製作。

評估板安裝有四通道、低功耗、12 位元、 180 MSPS、TxDAC?AD9106 和波形產生器。 該 DAC 的高採樣速率非常適合 1 MHz 至 40

#### Analog & Power

圖 2: AD9106 功能框圖。

MHz 範圍内的超音波工作頻率,外部成像設備 通常使用 1 MHz 至 15 MHz 的頻率,而靜脈内 心血管設備使用高達 40 MHz 的頻率。此外, AD9106 高度整合,具有用於產生複雜波形的 晶片模式記憶體,以及使用 24 位元調諧字、支援 10.8 Hz/LSB 頻率解析度的直接數位頻率 合成器 (DDS)。該元件也是高度可編程的,四 個 DAC 通道中的每個通道的模式週期、 啓動延遲、增益和偏移都可以獨立改變。此外,其具有低功耗特性 (在 3.3 V、4 mA 輸出和 180 MSPS 下,每通道功耗 78.8 mW,總計 315.25 mW),這是超音波設備等大型多通道系統的一個重要考慮因素。

## 提高超音波設備的精度和圖像解析度

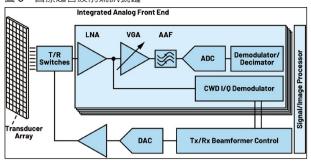

推車式超音波系統在圖像品質或解析度方面優於手持裝置,主要是因為通道數量差異巨大。然而,通道數量可能因製造商而異。成本和功耗是超音波設備等大型系統的重要考慮因素,因此業界使用了一些技術來儘量減小這兩個因素。在圖3所示的典型超音波訊號鏈中,如果我們考慮到每個發射器路徑(DAC+高壓放大器,驅動探頭尖端處換能器陣列中的一個元件)都對應一個接收器路徑(整合類比前端),那麼通道數的確定相對簡單。根據這個假設,我們可以說超音波系統中的通道數介於16到256之間。先進系統(其中大部分推車式)中的

## nalog & Power

圖 3:醫療超音波前端訊號鏈。

通道數為 64 或更多。對於可攜式、中低端系統, 16 至 64 個通道更為常見。

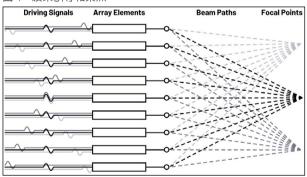

在超音波系統的發射器路徑中,聲能或聲 波束掃過身體。聲波由探頭前端處的壓電換能 器元件從電訊號轉換而來。如圖4所示,每個 電訊號或發射器訊號的相位和幅度均經過程式 設計,引導入射能量束沿著一條線進入身體。 從器官組織反射的聲波被換能器元件再次轉換 為電能。目標的位置或距離將根據換能器陣列 中元件之間的時間延遲顯示在螢幕上。因此, 為了顯示人體內部的準確圖像,同步或者能夠 控制發射器訊號之間的延遲十分重要。

圖 4:波束引導和聚焦。

## 多晶片同步的要求

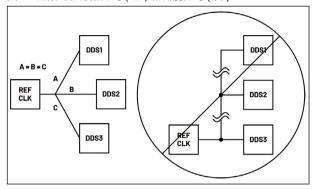

為了成功同步多個DDS DAC(如AD9106),必須控制差分時脈輸入(CLKP和CLKN)和TRIGGER接腳的降緣。

而為了滿足同步的第一個要求,PCB 佈局 應採用謹慎的時脈分配做法,請參見圖 5 所示。 這將充分減少 REF CLK 邊緣之間的相位差 (其

圖 5:建議時脈分配佈局(左)和次優佈局(右)。

會導致 DDS 輸出處出現成比例的相位差)。

模式產生由 AD9106 的 TRIGGER 接腳的降緣觸發,因此同步的下一個要求是確保TRIGGER 邊緣一致。圖 5 所示的佈局技術也可應用於從控制器的數位輸出佈線到每個AD9106 元件的 TRIGGER PCB 佈線。

## 利用 AD9106-ARDZ-EBZ 評估多晶 片同步

為了評估多個 AD9106 DAC 的同步,可以使用兩個 AD9106 評估板和一個 SDP-K1 控制器板。

#### 材料

- ■兩個 AD9106-ARDZ-EBZ 板

- ■用於電路板與 PC 連接的 USB 電纜

- SDP-K1

- ■一個 12 V 壁式電源轉接器

- ■訊號產生器

- ■可變長度 SMA 端接電纜

- ■一個 SMA 端接 T 型分路器

- ■母對母 Arduino 連接器導線

#### 硬體設定

連接三個電路板之前,配置兩個 AD9106-ARDZ-EBZ 板,使 DAC 輸出連接到板載放大器,並且 DAC 時脈由連接到 J10 的外部

#### Analog & Power

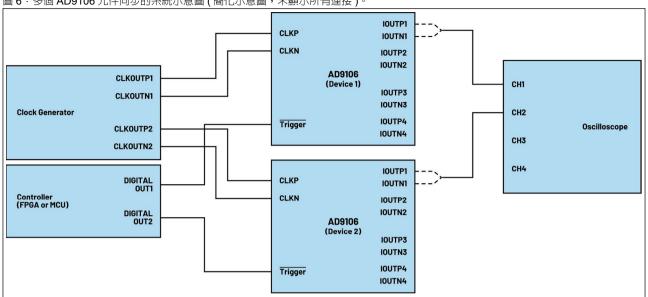

圖 6:多個 AD9106 元件同步的系統示意圖 (簡化示意圖,未顯示所有連接)。

源提供。關於 JP1 和 JP2 的正確連接,請參 閱 Eval-AD9106 Wiki 使用者指南 (https://wiki. analog.com/resources/eval/dpg/eval-ad9106) 中的圖 14b。另外,請設定其中一個 AD9106-ARDZ-EBZ 板,使板上元件的 CSB 接腳連接 到交替 GPIO 接腳 (安裝 R39 而不是 R38)。確 保 SDP-K1 的 VIO ADJUST 設定為 3.3 V。

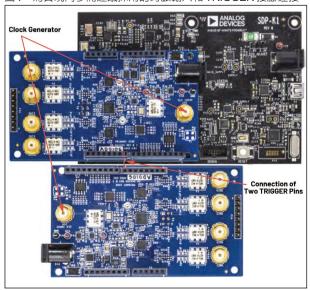

接下來應設定圖7所示每個板的時脈輸入 和 TRIGGER 接腳的連接,然後設定表 1 中的

圖 7: 為實現同步而建議採用的時脈輸入和 TRIGGER 接腳連接。

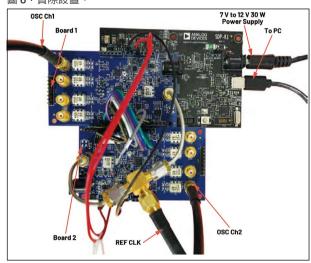

圖 8:實際設置。

其餘連接。將板 1 安裝到 SDP-K1 Arduino Uno 埠,然後將板2放置在與板1成180°的位置, 以使兩個板的 TRIGGER 接腳並排放置。這是 TRIG2 到 SDP-K1 數位輸出的最短連接,由此 TRIG1 和 TRIG2 路徑大致相等。

然後將高頻波形產生器的輸出連接到分離 式SMA端接T形分路器,其可以連接不同長 度的 SMA 端接同軸電纜。

應用了所有連接的實際設定如圖 8 所示。 表 1 總結了板對板連接。

### nalog & Power

表 1:SDP-K1 和兩個 AD9106-ARDZ-EBZ 板的板對板連接

| SDP-K1 Arduino Uno 連接器 |                                    | AD9106-ARDZ-EBZ 的相連網路 |               |

|------------------------|------------------------------------|-----------------------|---------------|

| 接腳編號                   | 接腳功能                               | 板 1                   | 板 2           |

| P2.1                   | NC                                 |                       |               |

| P2.2                   | IO_PWR_SUPPLY                      | IOREF                 | IOREF         |

| P2.3                   | MAIN_RESET                         | RESET                 | RESET         |

| P2.4                   | SDRAM_&_ARDUINO_PWR_SUPPLY (3.3 V) | 3.3 V                 | 3.3 V         |

| P2.5                   | +5V_CON                            | 5 V                   | 5 V           |

| P2.6                   | GND                                | GND                   | GND           |

| P2.7                   | GND                                | GND                   | GND           |

| P5.1                   | ARDUINO_GPIOO/RX                   | VIN                   | VIN           |

| P5.2                   | TX + 1                             |                       |               |

| P5.3                   | GPIO2                              | EN_CVDDX              | EN_CVDDX      |

| P5.4                   | GPIO3/PWM                          |                       |               |

| P5.5                   | GPIO4                              | SHDN_N_LT3472         | SHDN_N_LT3472 |

| P5.6                   | GPIOS/PWM                          |                       |               |

| P5.7                   | GPIO6/PWM                          |                       |               |

| P5.8                   | GPIO7                              | TRIGGERB              | TRIGGERB      |

| P4.1                   | GPIO8                              | RESETB                | RESETB        |

| P4.2                   | GPIO9/PWM                          | SPI_CSB_ALT           |               |

| P4.3                   | GP1010/PWM/CS                      | SPI_CSB_DFLT          |               |

| P4.4                   | GPIO11/PWM/MOSI                    | STD_SPI_MOSI          | STD_SPI_MOSI  |

| P4.5                   | GPIO12/MISO                        | STD_SPI_MISO          | STD_SPI_MISO  |

| P4.6                   | GPIO13/SCK                         | STD_SPI_SCK           | STD_SPI_SCK   |

| P4.7                   | GND                                | GND                   | GND           |

| P4.8                   | AREF                               |                       |               |

| P4.9                   | SDA                                |                       |               |

| P4.10                  | SCL                                |                       |               |

#### 軟體

這裡提供了在 Mbed 開源軟體上開發的示 例原始程式碼。關於這些原始程式碼的詳細說 明可參考wiki頁面,依此,開發者只需稍加修 改,即可透過 SPI 對兩個評估板上的每個元件 進行獨立編程。暫存器值以及程式碼的其他部 分可以輕鬆客製,具體而言是示例3中的暫存 器值 (DDS 產成的正弦波,具有不同的啓動延 遲和數位增益設置。修改程式碼後,便可使用 Mbed 線上編譯器將產生的二進位檔案拖放到 SDP-K1 驅動器中,此同樣的過程也適用於其 他應用。

#### Analog & Power

#### 說明

如圖 6 的簡化圖所示,元件間的輸出同步 是透過測量多個元件的同一 DAC 輸出通道(即

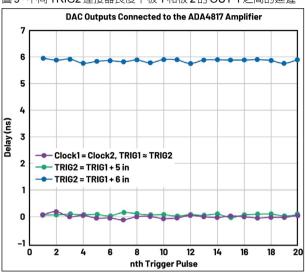

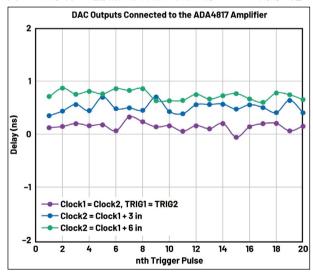

圖9:不同TRIG2連接器長度下板1和板2的OUT1之間的延遲。

圖 10: 不同時脈 2 連接器長度下板 1 和板 2 的 OUT 1 之間的延遲。

通道 1) 之間的延遲來實現的。相對於 TRIG1 (控制器板到板 1) 改變 TRIG2 (控制器板到板 2) 的連接器長度,以及相對於時脈 1 (時脈發生器到板 1) 改變時脈 2 (時脈產生器到板 2) 的連接器長度,此兩種情況對於同步的影響可以透過示波器來進行觀察。

#### 結果

圖 9 記錄了改變觸發連接器長度時的測量結果,而圖 10 則記錄了改變時脈連接器長度後的測量結果。

如果 TRIGGER 接腳所連接的數位輸出具有與 STM32F469NI (SDP-K1 上的微控制器)類似的驅動特性,那麼 TRIGGER 佈線容差只要在 5 英寸以内,就能維持元件間的同步。

匹配的時脈輸入佈線將導致最短元件到元件的輸出延遲,但根據特定系統中可容忍的延遲,則可相應地調整時脈佈線長度容差。

## 結語

在超音波設備製造中,利用 AD9106 評估平台提供的設計彈性和客製化優勢可以縮短開發流程和上市時間。無需設計新的發射子系統原型即可評估多個發射 DAC (如 AD9106)的同步。透過使用兩個 AD9106-ARDZ-EBZ 板、一個 SDP-K1 控制器板並對示例 Mbed 代碼進行少量修改,就能實現對同步的評估。 44

## COMPOTECHAsia 檢書

每週一、三、五與您分享精彩内容

https://www.facebook.com/lookcompotech