Analog & Power

# 採用創新數位預失真技術

# 進行 ADC 和音訊測試的高性能訊號源

測試精密儀器儀錶需要使用超低失真、低雜訊、高性能的訊號產生器。新產品通常需要保證性能指標在較高的水準。有些參考設計 (例如 ADMX1002) 利用高性能精密數位類比轉換器 (DAC) 簡化了這一任務,這些轉換器具有卓越的精度和解析度水準。1 此外,加入一種創新數位預失真演算法可以進一步增強測試訊號的保真度,從而以低成本的小尺寸實現卓越的低失真訊號。

■作者: Gustavo Castro / ADI 系統應用工程師

#### 簡介

隨著精密類比數位轉換器 (ADC) 和高傳真音訊裝置 (CODEC、MEMS 麥克風等)不斷發展,越來越需要在自動化測試設備 (ATE) 中產生高性能的音訊和任意訊號。要描述、驗證和測試這些裝置的直流和交流特性需要使用多種高性能儀器儀錶,這導致開發和生產測試成本增加,有時會令人望而卻步或限制測試覆蓋範圍。

在可能的情況下,測試工程師會開發內部解決方案作為替代方案,但這種做法非常耗費時間和資源。有些參考設計,例如 ADMX1002 超低失真訊號產生器模組,目的在提供一種替代方案,以加快這一開發過程。

圖 1: ADMX1002 超低失真和低雜訊訊號產生器。

ADMX1002 解決了硬體和嵌入式軟體發展挑戰。除了透過簡單的序列介面簡化設計複雜性以外,它還可以自動產生多個正弦波和任意波形。此外,透過採用創新的數位預失真演算法,ADMX1002 進一步提高了訊號鏈中的DAC 和放大器性能。

# 高性能混合訊號測試需求

現代 ADC 和其他混合訊號元件經常需要使用一個源來測試高性能直流和交流特性。在所有情況下,源的性能都必須優於被測裝置(DUT)的性能。

執行直流測試是為了確保無失碼,並且驗證差分非線性 (DNL)、積分非線性 (INL)、偏置和增益誤差。這些測試需要利用低雜訊和高解析度的直流耦合單發線性訊號 (例如斜坡訊號)來表徵 INL和 DNL 性能。在這種類型的測試中,需要達到高解析度,以便執行 ADC 中的所有可用代碼。

交流測試驗證總諧波失真 (THD)、訊噪失 真比 (SINAD) 和無雜散動態範圍 (SFDR) 等參 數。這些測試通常使用超高品質的訊號音 (正 弦波) 進行,這表示其中不能包含高於目標規

## nalog & Power

格的任何諧波成分。為了完成這項任務,測試工程師可以採用客製化濾波器來消除測試訊號中不需要的失真產物,但這會增加系統的複雜性和成本。但是,來自源的寬頻雜訊很難在相關訊號周圍進行濾波。來自源的雜訊需要低於被測 ADC 的雜訊基底,確保不會降低預期的測量目標。

下方的產品手冊匯總列出了高性能 ADC 的 發 佈 規 格:AD4020/AD4021/AD4022、ADAQ23878 和 AD7134,如表 1 所示。根據此表,可以看出,我們的目標是得出優於一123 dBc 的 THD。

表 1: 高性能精密 ADC 規格示例

| 參數          | AD4020 | ADAQ23878 | AD7134 |

|-------------|--------|-----------|--------|

| 解析度(位元)     | 20     | 18        | 24     |

| 採樣速率 (MSPS) | 1.8    | 15        | 1.5    |

| DNL, ppm    | 0.3    | 1         | 不適用    |

| INL, ppm    | 1      | 2.4       | 2      |

| SNR, dB     | 100.5  | 89.3      | 107    |

| THD, dBc    | -123   | -115      | -120   |

| SINAD, dB   | 100    | 89        | 106.5  |

| SFDR, dBc   | 122    | 114       | 125    |

# 低失真設計的關鍵考慮因素:解析度 和線性度

失真可以表示為在任何給定點上訊號幅度的誤差。這些誤差導致訊號偏離其理想的訊號形狀。對於數位合成訊號,想要準確表示相關訊號的每個樣本,關鍵在於採用真正的高解析度 DAC,保證線性度達到最低有效位元 (LSB)。由於 INL 和 DNL 是量化轉換器與其理想轉換函數之間的偏差的指標,這些線性度誤差會直接影響到高傳真訊號的再現。

由於週期訊號的失真通常用 THD 表示,我們需要量化解析度和 INL 對 THD 的影響,以選擇合適的精密 DAC。為了觀察低 THD,需要採用低雜訊基底,這表示需要高訊號雜訊 (SNR)。

從根本上說,轉換器的訊號雜訊受到量化雜訊 的限制。一般認為,訊號雜訊和解析度的關聯 運算式如下所示

$$SNR = 6.02 N + 1.76 + 10 \times log \left(\frac{f_S}{2 \times BW}\right) (dB)$$

(1)

其中 N 為轉換器中可用的位數, $f_s$  為取樣速率,BW 為測量頻寬。 $^2$  從表 1 可以看出,我們所需的訊號雜訊至少要優於 100.5 dB,最好是其 3 倍,約為 110 dB。假設頻寬達到第一個奈奎斯特區域,那麼在 110 dB 訊號雜訊時,所需的解析度為 18 位元。

接下來,我們需要量化 INL 和 THD 之間的關係。為此,我們假設 DAC 具有弱二階 INL。它的轉換函數可以用以下這個多項式表示

$$y = ax + bx^2 \tag{2}$$

其中 y 是 DAC 的輸出 (單位:伏特),x 是輸入代碼。第一項的係數 a 表示輸入代碼和輸出電壓的理想關係因數。第二項表示 INL,其係數 b 比 a 小得多。使用此 DAC 產生餘弦訊號  $\mathbf{x}(t) = \cos(\omega t)$ ,會導致在輸出中

$$y(t) = a \times \cos(\omega t) + b \times \cos^2(\omega t) \tag{3}$$

因為三角恆等式

$$\cos^2(\theta) = \frac{1}{2} \left[ \cos(2\theta) + 1 \right] \tag{4}$$

可以將 DAC 輸出端的訊號表示為

$$y(t) = \frac{b}{2} + a \times \cos(\omega t) + \frac{b}{2} \times \cos(2\omega t)$$

(5)

第二項現在顯示第二次諧波失真 (HD2)。這種關係顯示,INL會對產生低失真訊號產生基本限制。這一分析也適用於產生高階諧波失真分量的高階 INL項。例如,增加幅度 c 的三階非線性項,導致在訊號 3 中:

$$y(t) = \frac{b}{2} + \left(a + \frac{3c}{4}\right)\cos(\omega t) + \frac{b}{2} \times \cos(2\omega t) + \frac{c}{4} \times \cos(3\omega t) \quad (6)$$

假設我們採用 18 位元 DAC (根據訊號雜

#### Analog & Power

訊計算),以及 2 LSB 三階 INL,那麼三階諧波 導致的失真預計為

$$HD3 = 20 \log \frac{\frac{c}{4}}{a} = 20 \log \frac{\frac{2}{4}}{218} = -114.4 \, dBc$$

(7)

這與我們優於 —123 dBc 的設計目標相差 甚遠。再增加兩個位元,可以將此失真再降低 12 dB,達到 —126 dBc。這表示要實現我們的 失真目標,至少需要 1 個具有 20 位元解析度的 DAC。

#### 訊號產生路徑的設計

要設計一個能夠滿足失真和雜訊要求的源,首先需要幾個關鍵元件:DAC 和其基準電壓電路。可以使用 AD5791 20 位元精密 DAC達成這一目標。它的高解析度和線性度優於 1 LSB,保證在使用 10 V 輸出電壓時,能夠以高準確度再現誤差小於 10 µV 的訊號位準。

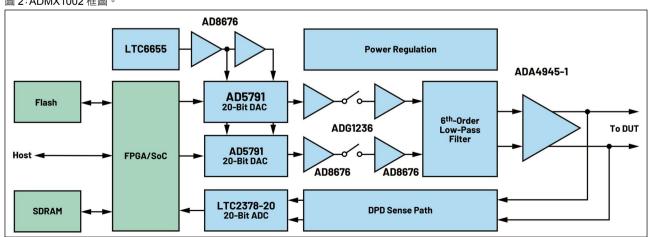

輸出訊號路徑的簡化示意圖如圖 2 所示。兩個 AD5791 採用相反的極性來實現全差分路徑,進一步提升訊號雜訊,並從接地引起的串擾中解耦相關訊號。低雜訊基準電壓源(例如LTC6655)和 AD8676 精密運算放大器結合,提供每個 AD5791 的高線性雙極運行所需的正負基準電壓位準。

由於 AD5791 採用高精度結構,在使用精密 DAC 產生訊號時,遇到的常見挑戰在於代碼轉換期間產生的毛刺能源。4 毛刺會使產生的訊號的時域特徵變形,給 DUT 提供多餘的能量。對於週期訊號,這些毛刺會在頻域中產生與基頻訊號音諧波相關的雜散成分。要解決這一個問題,可以對毛刺能量進行濾波,這會大幅降低訊號頻寬和源的建立時間。有一種更好的解決方案是基於採樣保持電路 5 進行去毛刺電路,且採用低電荷類比注入開關,例如 ADG1236和 AD8676 運算放大器。

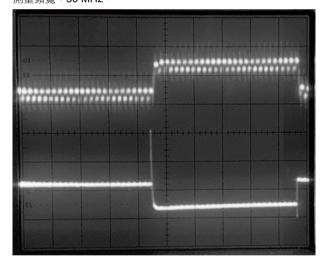

圖 3 顯示在使用去毛刺電路之後(頂部)和之前(底部)的10 kHz 方波。底部曲線顯示圖3: 去毛刺電路操作。時間尺規:5 μs/div 靈敏度:5 mV/div 測量頻寬:50 MHz。

圖 2:ADMX1002 框圖。

#### nalog & Power

AD5791 輸出端出現的代碼轉換毛刺。DAC 和去毛刺電路的更新速率為 1 MHz。來自開關的剩餘電荷注入與產生的訊號不是諧波相關的,可以被輸出端的重構濾波器輕鬆濾波。

從去毛刺電路產生的訊號在到達輸出端之前,會被一個採用 ADA4945-1 全差分放大器 (FDA) 的多級六階低通濾波器濾波。這種高階重構濾波器用於消除來自去毛刺電路以及超出第一個奈奎斯特區域的鏡像中的剩餘能量,該能量可能重新混疊到 DUT 的輸入頻譜中。6 ADA4945-1 採用差分輸出來滿足現代 ADC 的輸入要求。此外,每個 ADA4945-1 只貢獻 1.8 nV/√ Hz 雜訊,透過得到保證的 0.5 μV/°C 失調漂移實現高精度。

#### 數位預失眞

數位預失真 (DPD) 技術用於盡可能降低訊 號路徑中的分量帶來的非線性度。DPD 需要事 先知道需要修正的誤差值,以便在操作過程中 從訊號中減去這些誤差。所以,必須首先對訊 號路徑進行測量。

測量訊號路徑誤差時的挑戰在於測量路徑 的失真需要低於源路徑;否則,來自測量路徑 的誤差將會增加到源中,使其性能降低。即使 使用優質的 ADC 和放大器,這也很難實現。例如,作為一款 20 位元 ADC,LTC2378-20 具有業界較高的内在線性度,可以保證 ± 2 ppm INL,這是 AD5791 的 INL 的 2 倍。這表示不可能透過簡單將轉換函數的多個點數位化來測量源路徑的轉換函數誤差。我們需要一種更好的方法。

ADMX1002採用一種專利 DPD 演算法,提高了用於糾正源誤差的測量路徑的線性度。因為目標是降低正弦波形的失真,所以源會在測量階段產生一個單頻訊號音。位於 ADC 之前的 DPD 感測路徑增強了基於這種訊號的路徑的總體線性度。

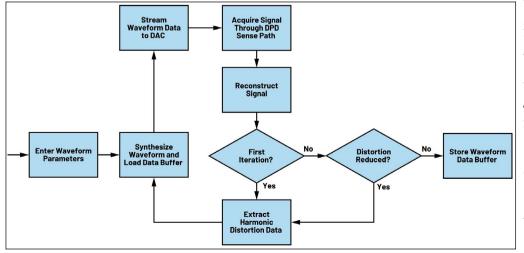

利用波形的多個數位化段來重建數位域中的訊號,然後與數學模型進行比較。從該操作中提取校正參數,並將其用於產生正弦波。這個過程需要進行多次反覆運算,以排除可能破壞結果的隨機誤差。一旦該演算法確定了最佳校正,它會停止,並將最後一次反覆運算中使用的參數儲存起來,用於訊號產生。該演算法的簡化流程圖如圖 4 所示。

由於該校正特定於正在產生的訊號,所以 必須為具有不同幅度和頻率的任何其他訊號執 行此分析。為了縮短在 ATE 系統中設定不同

> 可以將處理後的波 形資料儲存在板載 快閃記憶體中, 以便隨時調取。 ADMX1002可以儲存多達15種不包括 的波形,也包括雙式。

波形所需的時間,

沒有 DPD 的 訊號鏈的失真和雜

圖 4: ADMX1002 中採用數位預失真產生的波形。

#### Analog & Power

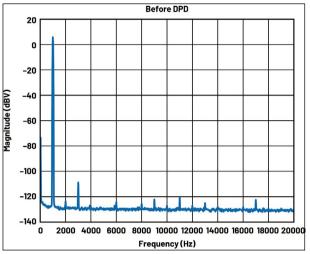

圖 5: ADMX1002 的頻譜,產生 2 V rms, 1 kHz,不具有 DPD。

圖 6: ADMX1002 的頻譜,產生 2 V rms, 1 kHz,具有 DPD。

訊性能如圖 5 的頻譜所示。在同樣的裝置中,DPD 演算法的效果如圖 6 所示,其 THD 總值超過 —130 dBc。比起不具有 DPD 的硬體得出的 —115 dBc,實現了 15 dB 改善。

除了 DPD 演算法,幅度校正演算法使用 DPD 感測路徑來補償重構濾波器對源路徑施加的衰減。

整個系統的處理、連接和控制均是透過 SoC 執行的,其中包括具有 Arm 核心處理器的 FPGA 結構。執行的任務包括:

- ■波形頻率合成

- ■預失真演算法執行

- ■非揮發件模式記憶體管理

- ■去毛刺電路的精準時間控制

- ■資料流程傳輸到數位類比轉換器

- ■類比前端開關的控制

- ■電源軌控制和排序

- ■主機介面: SPI、狀態、並行控制

額外的 DDR3 SDRAM 支援 SoC 處理任務,例如直接將資料流程傳輸至資料轉換器。

#### 爲系統供電

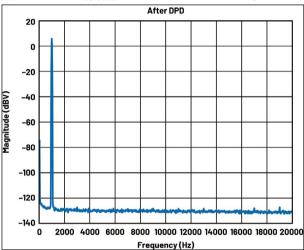

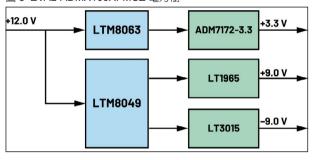

在將所有元件組合在一起時,硬體設計師始終會面臨在整個系統中佈設高性能電源軌的現實問題。數位元件通常需要在負載點調節多個低壓電源軌,而類比和混合訊號元件需要與數位元件的功率轉換適當解耦,並使用低雜訊電源軌供電。為了簡化這一項任務,ADMX1002整合一個完整的電源子系統,由低壓差 (LDO) 調節器和電力監控器組成,從而無需產生多個電源軌。

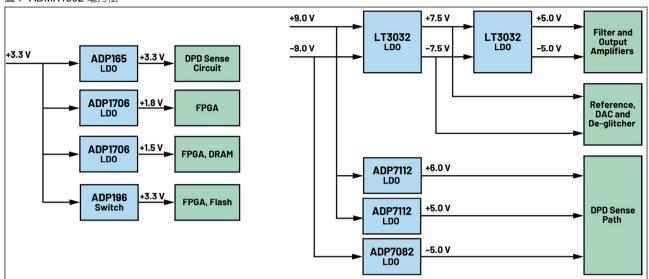

LDO 調節器消除了來自上游開關模式電源的多餘漣波,防止敏感的類比電路拾取原本會在輸出頻譜中觀察到的雜散。此外,SoC 的關鍵電源軌是使用 LTC2962 來監控的,該元件可以產生電源良好訊號,供主機系統輪詢以用於診斷。總體來說,ADMX1002 只需要主機提供三條大功率電源軌:+3.3 V、+9.0 V和一9.0 V。簡化的電力樹如圖 7 所示。

使用 LTM8049 之後,從正極電源軌 (例如電腦測試系統中的常用電源軌 +12 V)產生低雜訊 ±9.0 V電源軌的操作會很簡單,無需使用外部磁性元件或複雜的佈局。同樣,可以使用 LTM8063 將電壓從 +12 V降低至 +3.3 V。可以使用額外的 LDO 穩壓器 (例如 ADM7172-3.3、LT1965 和 LT3015)確保漣波電流不會流入精巧型 ADMX1002 中,保持乾淨的輸出頻譜。該配置如圖 8 中的框圖所示,在 EVAL-

## nalog & Power

#### 圖 7:ADMX1002 電力樹。

圖 8: EVAL-ADMX100XFMCZ 電力樹。

ADMX1002FMCZ 評估板得到採用。

#### 結論

本文證實,利用精心設計的訊號路徑和訊號處理技術可滿足對 ADC 和音訊測試的要求。要實現這一個目標,需要使用高解析度 DAC,注意確保沒有毛刺進入輸出,並進行具有低失真放大器的重構濾波器。透過進行利用混合訊號演算法優化的數位回饋路徑,可以進一步改善性能,以實現準確的訊號重構。此外,可以透過一種創新的數位預失真演算法提取諧波失真資訊,其可用於合成波形,以補償源路徑中的失真。

#### 參考電路

<sup>1</sup> Patrick Butler,「近乎完美的 DDS 正弦波訊號

- 音產生器」。ADI,2019年12月。

- Walt Kester,「MT-001 教程:揭開一個公式 (SNR = 6.02 N + 1.76 dB) 的神秘面紗,以及 為什麼我們要予以關注」。(ADI,2009 年)

- <sup>3</sup> Behzad Razavi,《射頻微電子學》,第 2 版。 2011 年 9 月。

- <sup>4</sup> Miguel Usach 和 Martina Mincica,「AN-1444 應用筆記:精密 DAC 連續更 新需考慮的二 階效應」。ADI,2017 年 1 月。

- 5「MT-090 教程:採樣保持放大器」。(ADI, 2009 年)

- <sup>6</sup>「為何 DDS 需要配備重構濾波器?」Analog Devices. Inc.

- ■Brandon、David 和 Ken Gentile,「AN-837: 基於 DDS 的時脈抖動性能與 DAC 重構濾波 器性能的關係」。ADI,2006 年 12 月。

- Kester, Walt.「MT-003 教程:瞭解 SINAD、ENOB、SNR、THD、THD + N、SFDR,不在雜訊基底中迷失」。(ADI, 2009 年)

- Kester, Walt.「MT-017 教程:過採樣插值 DAC」(ADI, 2009 年) எ