# 理清 ADC 五大架構特點

ADC 是什麼？我們為什麼需要 ADC？ADC 有哪些架構？他們的工作原理和特點是什麼，分別適用於哪些場景？今天，我們就來逐一解密！

■文：Monolithic Power Systems (MPS)

## 一、ADC 是什麼？

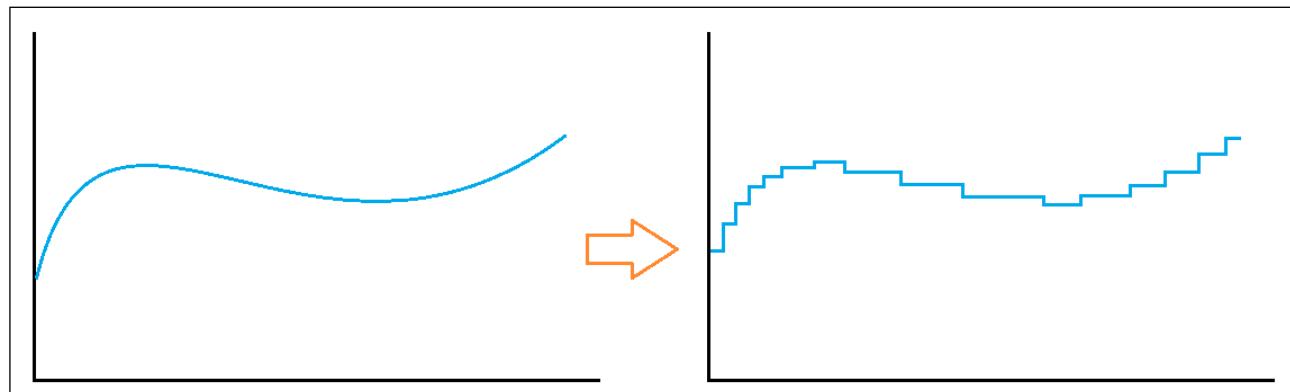

ADC 的英文全拼是 Analog to Digital Converter，中文為模數轉換器，它可以將連續類比輸入信號轉換為離散的數位信號，並以一序列 1 和 0 的形式進行傳送。這些輸入信號被量化為數位量後，再進行傳輸或進一步後續處理時，就不易受雜訊干擾。

**類比信號：**連續變化的物理量所表達的資訊，如溫度、濕度、壓力、長度、電流、電壓、光強、音色等。

**數位信號：**引數和因變數都是離散的資料資訊，通常容易被 MCU/DSP/CPU 進行後續處理的二進位數字來表達。

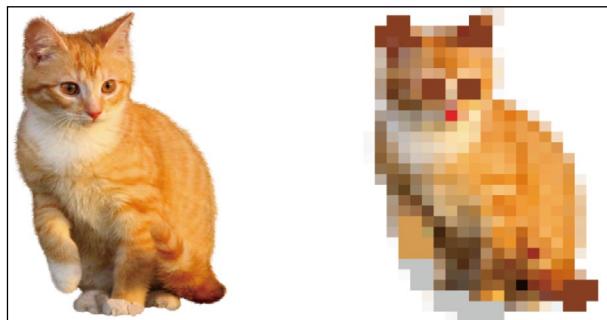

從類比到數位的變換就像從真實世界進入到圖元世界，我們日常生活中常講到的數位相機、手機上的攝像頭模組內，就包含一個成像專用的 ADC，將圖像中每個圖元單元的類比光強度值轉換成數位量。

## 二、我們為什麼需要 ADC？

現實世界中，我們被溫度、濕度、光、聲等物理量包圍，作為有著感知能力的生物體，我們能夠非常自然地獲取類比信號，並與這些物理量達成默契，但是對於 CPU、MCU 等各類電子設備來說，這些信號卻很難被理解。

在數位化社會中，一切事物都被賦予了可量化的期待，對資料的讀取、處理、傳輸和存儲，成為了人類認識事物的基本邏輯。

因此，我們需要將現實世界中的類比信號轉換為機器能夠理解的數位表達。現實世界和數位

世界的“窗戶紙”將由模數轉換器(ADC)來捅破。

### 三、ADC 有哪些架構？工作原理是什麼？

ADC 架構有：並行比較型 (Flash)，逐次逼近型 (Successive Approximation Register)，積分型 (Integrating)，增量型 (Delta-Sigma)，流水線型 (Pipeline) 等。

#### 1. 並行比較型 (Flash)

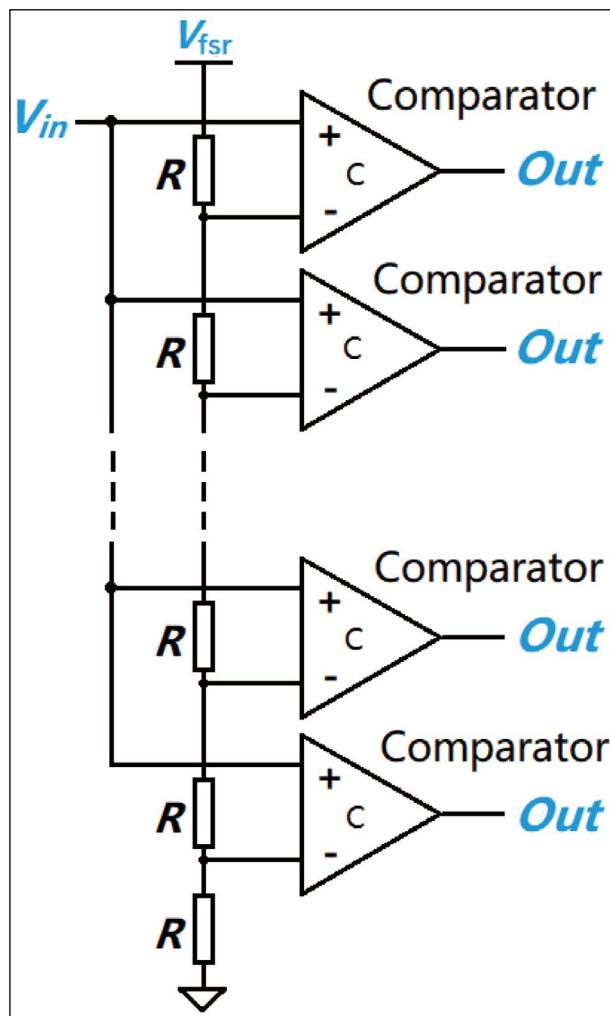

下圖是並行比較型 ADC 的拓撲原理圖，採樣輸入信號和設置好的比較電平直接比較得到輸出。

圖說：並行比較型 ADC 的拓撲原理圖

圖中假設有  $n$  個比較器，最下面的是第 1 個，滿量程輸入電平是  $V_{fsr}$ ，作為參考電壓，由  $n+1$  個等值電阻將其均分為  $n$  個階梯，那麼第  $X$  個比較器負向輸入電壓為  $V_{fsr} \cdot X/(n+1)$ ，如果從第  $m$  個比較器開始以上的比較器輸出都是 0，以下的輸出都是 1，那麼輸入信號電壓為：

$$V_{in} = V_{fsr} \cdot m/(n+1)$$

#### 2. 逐次逼近型 (SAR)

一個  $n$  位解析度的 SAR 型 ADC，第一階段，輸入信號先和設定好的比較電平輸入比較器作比較，比較電平設置為 ADC 滿量程的一半  $V_{fsr} \cdot 2^{-1}$ ，輸出第一位二進位結果  $B_1$ ，將  $B_1$  存入寄存器，第二階段，輸入比較器的比較電平根據第一次的比較結果設置為  $V_{fsr} \cdot 2^{-1} + (2 \cdot B_1 - 1) V_{fsr} \cdot 2^{-2}$ ，此處的  $B_1$  及後面公式中的  $B_2, B_3, B_{n-1}, B_n$  均作為十進位數字參與計算，比較後輸出第二位結果  $B_2$ ，同樣存入寄存器，進入第三階段，比較電平設置為  $V_{fsr} \cdot 2^{-1} + (2 \cdot B_1 - 1) V_{fsr} \cdot 2^{-2} + (2 \cdot B_2 - 1) V_{fsr} \cdot 2^{-3}$ ，得到第三位結果  $B_3$ ，直至第  $n$  階段，比較電平設置為  $V_{fsr} \cdot 2^{-1} + (2 \cdot B_1 - 1) V_{fsr} \cdot 2^{-2} + (2 \cdot B_2 - 1) V_{fsr} \cdot 2^{-3} + \dots + (2 \cdot B_{n-1} - 1) V_{fsr} \cdot 2^{-n}$ ，得到最後一位結果  $B_n$ ，由最高位  $B_1$  至最低位  $B_n$  組成的  $n$  位二進位數字即為該  $n$  位 ADC 的輸出結果，轉化為 10 進制數  $D$ ，那輸入信號的電平測量值等於  $V_{fsr} \cdot D \cdot 2^{-n}$ 。

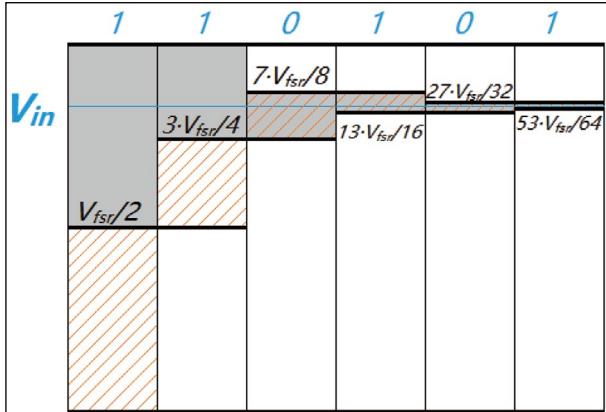

例如下圖是一個 6bit 的 SAR 型 ADC 的轉化流程，輸入信號先和  $V_{fsr}/2$  比較得到最高位 1，之後再和  $V_{fsr}/2 + V_{fsr}/4$  比較得到第二位 1，繼續下去，得到二進位結果 110101，根據上文的公式  $V_{fsr} \cdot D \cdot 2^{-n}$  得出輸入電平為  $53 \cdot V_{fsr}/64$ ，理論誤差小於  $V_{fsr}/64$ 。

#### 3. 積分型 (Integrating)

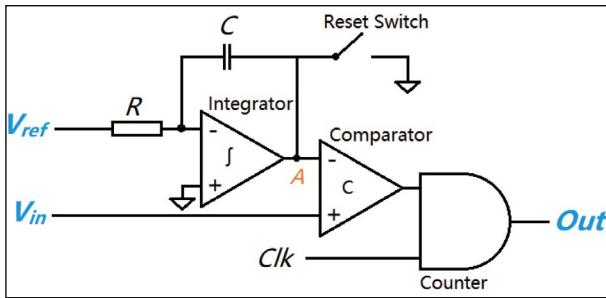

下圖是單斜率積分型 ADC 的拓撲原理圖，

圖說：一個 6bit 的 SAR 型 ADC 的轉化流程

通過積分器從 0 電平積分到達採樣信號電平的時間計算得到採樣電平。

圖說：單斜率積分型 ADC 的拓撲原理圖

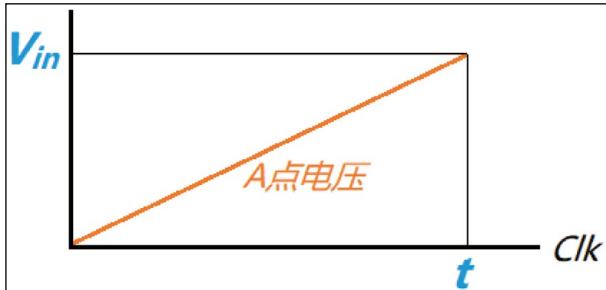

採樣開始時，積分器開始積分，同時計數器開始對輸入的時鐘信號 Clk 計數，假設該時鐘頻率為  $f$ ，積分電流為  $V_{ref}/R$ ，經過時間  $t$  後 A 點電壓超過輸入信號的電壓值，比較器輸出從 1 跳變至 0，計數器停止計數，得到計數值  $k$ ，通過下方公式計算得到輸入電壓。

$$V_{in} = (V_{ref}/R) \cdot k/(C \cdot f)$$

另外還有雙斜率積分型 ADC，分時將輸入電平和參考電平分別做正向和反向積分，可以

圖說：採樣開始時，積分器開始積分

更好的消除積分電路帶來的誤差，但是會增加一次積分時間，轉換速度會更慢。

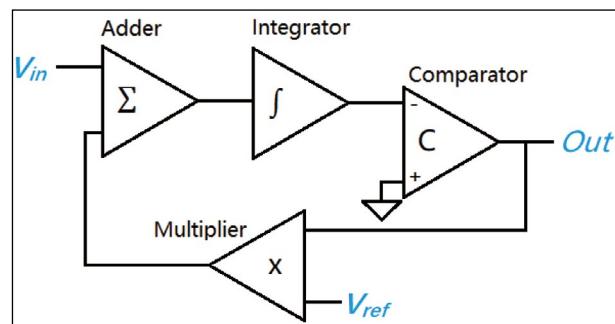

### 4. 增量型 (Delta-Sigma)

增量型 ADC 的拓撲原理圖如下，先看積分器，如果輸出小於 0，比較器輸出 1，否則輸出 -1，比較器輸出 1 時，乘法器輸出  $V_{ref}$ ，否則輸出  $-V_{ref}$ ，所以當積分器輸出大於 0 時，將有  $V_{in} - V_{ref}$  輸入到積分器中進行下一次比較，否則輸入  $V_{in} + V_{ref}$ ，記錄每一次比較器的輸出，統計輸出 -1 的次數  $X$  和總比較次數  $m$ ，通過下方公式來計算輸入電平，總的比較次數越高，解析度越高。

$$V_{in} = V_{ref} \cdot (2 \cdot X - m)/m$$

圖說：增量型 ADC 的拓撲原理圖

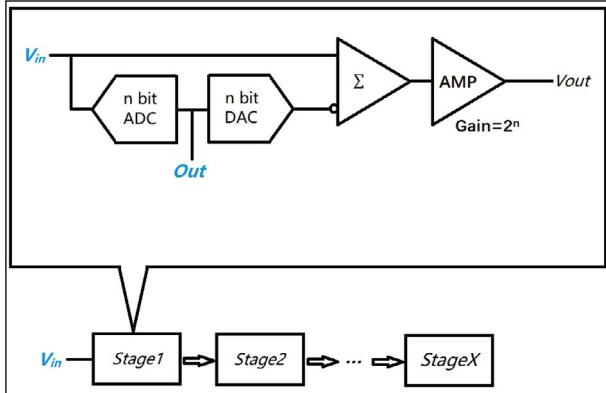

### 5. 流水線型 (Pipeline)

流水線型 ADC 通常由多個相同結構的子單元組成，每個子單元包含一個 ADC，一個反向 DAC，一個減法器，一個固定增益的放大器構成，子單元中的 ADC 多為 Flash 型，也有 SAR 型。

如下圖，假如一個  $X$  階的理想化流水線 ADC，子單元中的 ADC 的精度為  $n$  bit，該子單元滿量程為  $V_{fsr}$ ，假設該子單元  $m$  輸入信號  $V_{in}$  被該子單元內 ADC 量化的結果為  $A_m$ 。

$V_{fsr}$ ，那麼該單元可輸出的結果最小值  $A_{min}=0$ ，最大值  $A_{max}=(2^{-n}-1)/2^n$ ，將  $V_{in}$  和該量化結果通過 DAC 轉化為類比信號後送入減法器會得到一個小於等於  $V_{fsr} \cdot 2^{-n}$  的差值  $V_{in} - A_m \cdot V_{fsr}$ ，該差值通過子單元內增益為  $2^n$  的放大器放大後得到

圖說：一個 X 階的理想化流水線 ADC，經過 X 階最終會產生一個  $X \cdot n$  位精度的量化結果

電平為  $2^n \cdot (V_{in} - A_m \cdot V_{fsr})$  的類比信號輸出該單元，再作為輸入進入下一級子單元  $m+1$ ，經過同樣的流程得到量化結果  $A_{m+1} \cdot V_{fsr}$ ，每一級將輸入信號和量化信號的差值放大後送至下一級再做量化，經過 X 階最終會產生一個  $X \cdot n$  位精度的量化結果，由以下公式計算，

$$V_{in} = V_{fsr} \cdot (A_1 + A_2 \cdot 2^{-n} + A_3 \cdot 2^{-2n} + \dots + A_X \cdot 2^{-(X-1)n})$$

以上是理想狀態，而實際情況是前級 ADC 的失調誤差會導致輸入信號和 DAC 輸出的差值超出 0 到  $V_{fsr} \cdot 2^{-n}$  的範圍，此時  $2^{-n}$  的增益會導致輸入到下一級的信號超出量程範圍，為解決這個問題一般的做法是將放大器的增益降為

表 1:ADC 五大架構對比

| 架構類型        | 速度               | 精度            | 特點和適用場景                                                                                           |

|-------------|------------------|---------------|---------------------------------------------------------------------------------------------------|

| Flash       | 極快，通常在 1GHz 或以上  | 低 (10bit 以下)  | 用輸入信號和參考直接比較來得出結果，因此速度極快，但每提升 1bit 的精度，需要增加一倍的電路規模，導致精度很難做高，功耗較大，適用於精度要求不高但是採樣速度有非常高要求的場景。        |

| SAR         | 較快，通常在 1MHz 或以上  | 較低 (8-16bit)  | 由於有輸入保持電路的存在使之存在較大輸入電容，需要較強的輸入能力，功耗較低，適合於採樣速度有一定要求但是精度要求不高的場景。                                    |

| Integrating | 極慢，通常在 1kHz 以下   | 很高 (16bit 以上) | 由於需要較長的積分時間，精度越高的轉換時間也越長，適用於採集低頻或直流信號的場景。                                                         |

| Delta-Sigma | 較慢，通常為幾 kHz      | 很高 (16bit 以上) | 通過過採樣和雜訊整形實現高精度，同時降低了採樣速率，功耗較大，適合於低頻或直流信號的高精度採樣。                                                  |

| Pipeline    | 很快，通常在 100MHz 以上 | 較高 (10-16bit) | 由於每一級可以獨立運行，因此平均轉換速度很快，但是每一次信號採樣從輸入到輸出需經歷每一級才能得到結果，造成了精度越高延遲較高的缺點，功耗較大，適用於取樣速率和精度要求都較高但對延遲不敏感的場景。 |

$2^{-n-1}$ ，利用後一級的冗餘測量範圍來校正上一級的誤差。

每一級在完成當前流程後新的信號便可以輸入進行新的量化，因此平均轉換時間僅相當於信號走完單個子單元的時間  $t$ ，所以平均轉換速度會很快，但是每個信號需要通過所有級才可以得到最終結果，因此當一個信號輸入到得到結果至少需要時間  $Xt$ ，因此流水線型 ADC 是一種轉換快，但是高精度的會有較高的延遲。

## 四、ADC 五大架構對比

五大架構對比請看下表

## 附錄：

關於單片機電源系統公司 (Monolithic Power Systems, Inc., 簡稱 “MPS”) 是一家無晶圓廠的全球性公司，提供高性能、基於半導體的電源電子解決方案。MPS 成立於 1997 年，公司擁有三大核心優勢：深厚的系統級知識、強大的半導體專業知識以及在半導體製程、系統整合和封裝領域的創新專有技術。這些綜合優勢使 MPS 能夠提供可靠、緊湊且集成化的解決方案，這些方案具有高能效、成本效益和環境責任性。CTA