2013年8月9日在嵌入式系統設計扮演吃重角色的FPGA(現場可編程閘陣列),長久以來一直以取代ASIC為口號,但在功耗與架構設計上遲遲難以突破,但近年雙雄Altera與Xilinx(賽靈思)相繼在20奈米甚至16/14奈米製程有了重大投資與架構創新,終於讓多年來的願景有了開疆闢土的契機。

Xilinx首款20奈米 ASIC等級UltraScale元件開始投片

美商賽靈思(Xilinx)繼28奈米產品之後,日前宣佈其20奈米元件再創兩項業界第一。賽靈思已開始投片業界首款20奈米可編程邏輯元件 (PLD) 和業界首款20奈米All Programmable元件。同時,賽靈思亦著手建置業界第一個ASIC等級可編程架構——UltraScale™。續賽靈思率先投片業界首款28奈米元件、推出首款All Programmable SoC、All Programmable 3D IC及SoC等級設計套件以來,這些宣佈的多項里程碑將進一步延伸其領先業界的成就。

圖說: 賽靈思UltraScale架構:業界第一個ASIC級可編程架構,可從20nm平面電晶體結構 (planar)製程向16nm乃至FinFET電晶體技術擴展,從單晶片(monolithic)到3D IC擴展。它不僅能解決整體系統傳輸量擴展限制的問題和時間延遲問題,而且直接解決先進節點晶片性能方面的最大瓶頸問題——互連。

賽靈思公司資深副總裁暨亞太區執行總裁湯立人表示:「賽靈思擬定了一個業界最積極的20奈米元件投片計劃,在高階元件方面,大幅領先最近競手對手一年以上;而在中階元件方面,則領先對手至少半年。再加上台積公司的製程技術和賽靈思的UltraScale架構,運用Vivado設計套件進行協同最佳化,我們相信賽靈思將超前一年將系統級效能與整合度提升1.5至2倍,這等同於領先對手一個世代。」

賽靈思認為一個創新的架構方案,需要管理每秒數百gigabit資料量的系統效能,以及在全線速下進行智慧型處理功能,並可擴充至terabit級流量和teraflop級的浮點運算效能。單憑提升每個電晶體或系統模塊的效能,或者增加系統的模塊數量,都不足以達到上述目標,因此必須從改善通訊、時脈、關鍵路徑和互連技術等根本面著手,以因應龐大的資料流、即時封包、DSP與/或影像處理等應用需求。

UltraScale架構提供一個可運用先進ASIC技術的完全可編程架構,藉此克服這些棘手的問題:

- 針對龐大資料流提供最佳化的寬型匯流排支援多重terabit資料流量

- 支援多區域的類ASIC時脈、電源管理和新一代安全功能

- 提供高度最佳化關鍵路徑與內建式高速記憶體,突破各種DSP與封包處理問題

- 針對第二代3D IC系統整合提供晶片之間的步進式頻寬功能

- 提供大量I/O與記憶體頻寬,能大幅降低延遲率及支援3D IC的記憶體最佳化介面

- 運用Vivado工具解決佈線壅塞的問題並進行協同最佳化,讓元件利用率超過90%,而且不會影響效能

首批UltraScale元件將擴充目前賽靈思領先市場的28奈米Virtex、Kintex FPGA以及3D IC系列產品陣容,並成為未來Zynq UltraScale All Programmable SoC的基礎。這些元件更將提供全新的高效能架構需求,實現新一代更智慧型的系統。全新的功能包括:

- 配備智慧封包處理與流量管理功能的400G OTN

- 支援智慧型波束成形技術的4X4 混合模式LTE 和WCDMA 無線電

- 支援具備智慧型影像增強與識別功能的4K2K 與8K 顯示器

- 針對情報監視及偵察(ISR)提供最高效能的系統

- 支援資料中心的各種高效能運算應用

支援UltraScale架構FPGA元件的Vivado設計套件早期試用版本現已供貨。首批UltraScale元件將於2013年第4季開始出貨。

Altera第10代FPGA和SoC實現突破性優勢

Altera公司推出第10代FPGA和SoC(單晶片系統),協助系統開發人員在性能和功率效益上實現了突破。第10代元件在製程技術和架構基礎上進行了最佳化,以最低功率消耗實現了業界最好的性能和水準最高的系統整合度。首先發佈的第10代系列包括Arria 10以及Stratix 10 FPGA和SoC,具有嵌入式處理器。第10代元件採用了業界最先進的製程技術,包括,Intel的14-nmTri-Gate製程和台積電(TSMC)的20 nm製程。

Altera資深產品行銷總監Patrick Dorsey表示:「我們的第10代產品將促進可程式設計邏輯在新市場中的應用,進一步加速FPGA向傳統ASSP和ASIC應用領域的拓展。我們對第10代元件進行了最佳化,支援客戶開發可高度訂製的解決方案,大幅的提高了系統性能和系統整合度,同時降低了營運成本。」

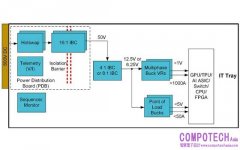

Stratix 10 FPGA和SoC設計支援最先進的高性能應用,包括網路、通訊、廣播以及電腦和儲存市場等應用領域,同時降低了系統功率消耗。Stratix 10 FPGA和SoC採用Intel 14 nm Tri-Gate製程和增強高性能架構,運作頻率超過了1 Gigahertz,兩倍於當前高階28-nm FPGA的核心性能。對於功率消耗預算非常嚴格的高性能系統,Stratix 10元件能在與前一代產品相當的性能水準上,協助客戶將功率消耗降低70%。

Arria 10 FPGA和SoC則是10代系列產品中最早推出的系列元件。該系列元件為中階可程式設計元件設立了新標杆,以最低的中階元件功率消耗提供當前高階FPGA的性能和功能。利用針對台積電20 nm製程進行了最佳化的增強架構,Arria 10 FPGA和SoC比前一代元件的性能提高了15%,而功率消耗降低了40%。Arria 10 FPGA和SoC含有28-Gbps收發器,頻寬比當前一代產品高4倍,系統性能提高3倍,包括支援2666 Mbps DDR4以及15-Gbps混合立方記憶體 (Hybrid memory Cube)。

早期試用客戶目前使用Quartus II軟體發展Arria 10 FPGA。Arria 10元件的第一批樣品將於2014年年初發售。Altera將於2013年 提供14 nm Stratix 10 FPGA測試晶片,2014年為Stratix 10 FPGA提供Quartus II軟體支援。