經過多次併購,新思科技 (Synopsys) 在設計前段到實體導入流程具備整合專業。董事長暨共同執行長 Aart J. de Geus 表示,隨著高科技向汽車、醫療多元範疇滲透,EDA 公司與相關業者除了深耕原本擅長的領域知識,還須向外跨界、相互學習,才能因應時代變局;Geus 以自家公司與 ARM 的合作為例,藉由簽署多年期協定,Synopsys 在晶片量產前就取得 ARM Cortex 處理器資訊及相關IP 授權,針對 ARM-based SoC 設計流程和工具進行優化,加速系統單晶片 (SoC) 的設計、實作和驗證時程。

照片人物:Synopsys 董事長暨共同執行長 Aart J. de Geus

Synopsys 亦可反向提供優化的腳本 (script) 給 ARM 的合作夥伴,確保取得 ARM Core 授權用戶,在進行設計專案時能受益於 Synopsys 優化的設計工具和方法論,並為 ARM IP 設計流程提供相關 Synopsys 設計工具的教育訓練,落實 FinFET 和絕緣層覆矽 (SOI) 等先進製程技術應用。雙方所勾勒的藍圖是:採用 ARM 處理器、程式庫、POP IP的參考實作,輔以 Synopsys Galaxy 工具,可實現晶片功耗、效能和面積的優化,涵蓋功能驗證、硬體模擬 (emulation) 和軟硬體除錯。Geus 表示,所有參與催生產品的業者都是主角、非一己之力可成。

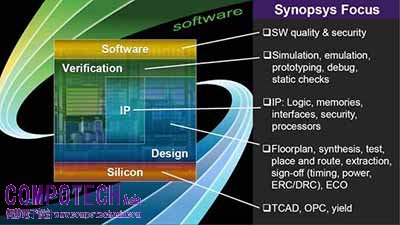

「從矽晶到軟體」全方位佈局

為此,Synopsys 計畫性展開「從矽晶到軟體」全方位佈局,尤其重視資安問題。其 DesignWare 的安全 IP 包括一系列加密核心、軟體庫、協定加速器、可信根、平台安全和內容保護 IP。近期針對智慧表、NFC 支付和嵌入式 SIM 等低功耗嵌入式應用所推出的 DesignWare ARC SEM110 和 SEM120D,具有增強記憶體保護單元和 SecureShield 技術,可簡化「可信執行環境」(TEE) 開發並透過 embARC 開放平台免費取得開源軟體——包括安全傳輸協議和 SecureShield 運行時庫,在特定背景下運行並在可信執行環境中管理容器分區和隔離,防止側通道攻擊。

圖1:Synopsys 奉行「從矽晶到軟體」的全方位佈局策略 資料來源:Synopsys 提供

ARC SEM 處理器帶有內嵌指令/資料加密和位址加擾的防篡改流水線及資料完整性檢查,能抵禦系統攻擊、IP 盜竊及資料外洩,且有監視計時器可檢測包括篡改在內的系統故障。基於可擴展的 32 位元 ARCv2 指令集體系結構 (ISA),ARC SEM110 處理器可作為 SoC 獨立安全內核,或劃分安全/非安全區的單一內核;ARC SEM120D 具 DSP 功能,可供醫療、感測處理和語音辨識等著重安全和即時處理的應用。除了被動防衛,另有混淆安全運行的統一指令時序、時序/能耗隨機化等先進安全功能,可故佈疑陣、避免駭客摸清真實運行情況。

在工具支援方面,DesignWare ARC MetaWare 開發套件可提供生成適用於深層嵌入式應用的高效代碼;ARC nSIM 快速指令集模擬器可支援初期軟體發展;ARC xCAM 可為軟體優化和系統驗證提供 100% 週期的精確模擬。為加速原型設計、軟體開發並將 IP 整合至 SoC,另有「IP 套件式解決方案」(IP Accelerated Initiative),為開發人員提供 IP 原型設計套件、IP 軟體開發工具組和客製化 IP子系統。

IC 設計追求高效 PPA 指標

針對 TSMC 28 HPC+ 及 16 nm FinFET製程,Synopsys 提供多項經矽晶驗證的DesignWare 介面 IP,包括:USB、PCI Express、DDR、MIPI、HDMI、SATA 與 Ethernet。由於介面 IP 和出色 PPA——功耗 (Power)、效能 (Performance) 及面積 (Area) 的設計工具實現能力,Synopsys 已連續六年獲頒台積電 (TSMC) 「年度最佳夥伴獎」。在先進節點製程上,Synopsys 已通過 TSMC 7 nm FinFET 的介面及基礎 IP 驗證,並完成 DesignWare 邏輯庫及嵌入式記憶體的客戶投片。另為因應 7 nm 超低電壓作業,Synopsys 推出 ASIC-based 的設計流程及方法論。

針對 TSMC 28 HPC+ 及 16 nm FinFET製程,Synopsys 提供多項經矽晶驗證的DesignWare 介面 IP,包括:USB、PCI Express、DDR、MIPI、HDMI、SATA 與 Ethernet。由於介面 IP 和出色 PPA——功耗 (Power)、效能 (Performance) 及面積 (Area) 的設計工具實現能力,Synopsys 已連續六年獲頒台積電 (TSMC) 「年度最佳夥伴獎」。在先進節點製程上,Synopsys 已通過 TSMC 7 nm FinFET 的介面及基礎 IP 驗證,並完成 DesignWare 邏輯庫及嵌入式記憶體的客戶投片。另為因應 7 nm 超低電壓作業,Synopsys 推出 ASIC-based 的設計流程及方法論。

圖2:Synopsys 認為應以系統觀看待「物聯網」 資料來源:Synopsys

它們包括:通路銅柱、多源樹合成和混合時脈網格,以及可配合關鍵網上阻力及電阻的自動化匯流排繞線等功能。「通路銅柱」是一種透過減少通路電阻與提升電子遷移強度來提高效能的新技術,可無縫融入用於 RTL 合成的 Design Compiler Graphical、用於佈局與繞線的 IC Compiler II;多源 CTS 和混合時脈網格在關鍵網上插入通路銅柱後,可經由全域與細部繞線調整訊號繞線插置通路銅柱,打造出具高客製化網格的低偏差與高效能時脈設計,以及針對時脈進行自動 H 樹建置 (H-tree creation)。

Galaxy 設計平台的數位及客製化實作工具、參考流程已通過 TSMC 7 nm 行動及高效能運算 (HPC) 設計認證,包括:繞線規則、IC Validator 實體驗證程序執行檔、PrimeTime 時序簽核、StarRC 萃取 (extraction) 技術檔案、與 SPICE 相關的統計時序分析,以及可相互操作製程設計套件 (iPDKs) 等;支援基於 Liberty Variation Format (LVF) 的參數晶片內變異 (POCV) 與先進波形傳播 (AWP) 技術,可處理 SADP 全彩 7 nm 流程的設計原則和要求,例如:具金屬裁切與多重曝光、更嚴苛的色彩感知電子遷移 (EM) 規則,保障各 SOC 設計層級穩定性。

表:Synopsys- TSMC 7 nm 可相互操作製程設計套件 (iPDKs)

|

套件名稱 |

用途 |

|

PrimeRail 和 CustomSim 穩定性分析 |

可支援色彩感知電子遷移規則及 IR 壓降 (IR-drop) 之準確靜態及動態閘層次及電晶體層次分析。 |

|

Custom Compiler 全客製解決方案 |

支援全著色工序。 |

|

軌道圖形 (track-pattern) |

支援、設計中 EM / IR 計算及 EM / IR 分析。 |

|

HSPICE、CustomSim 和 FineSim 模擬 |

透過自我加熱效應 (self-heating effect) 支援裝置建模,並針對類比、高頻與 SRAM 設計提供準確模擬結果。 |

|

NanoTime 客製時序分析 |

針對 7 nm 設備提供 SPICE 準確之電晶體層級的靜態時序分析。 |

|

ESP-CV 客製功能認證 |

對 7 nm SRAM、總體 (macros) 與元件庫 (library cell) 設計之電晶體層級的象徵對等性檢查 |

FinFET 製程及車用元件設計關竅多

Synopsys 對於車用領域亦未缺席。其 DesignWare 基礎IP (含邏輯庫及嵌入式記憶體) 已通過 TSMC 16 nm FFC (FinFET Compact) 及 28 nm HPC+ 製程驗證,符合嚴格車用 AEC-Q100 第一級溫度規範要求,協助設計人員快速取得先進駕駛輔助系統 (ADAS) 及車載娛樂系統 (infotainment) 等車用 SoC 的 AEC-Q100 認證。這些組合可提供 ISO 26262 ASIL B / ASIL D Ready 的認證、AEC-Q100測試 (testing) 及 TS 16949 品質管理。與此同時,Galaxy 設計平台的數位 (digital)、客製 (custom) 及簽核 (signoff) 工具套件的也已通過認證。

Synopsys 對於車用領域亦未缺席。其 DesignWare 基礎IP (含邏輯庫及嵌入式記憶體) 已通過 TSMC 16 nm FFC (FinFET Compact) 及 28 nm HPC+ 製程驗證,符合嚴格車用 AEC-Q100 第一級溫度規範要求,協助設計人員快速取得先進駕駛輔助系統 (ADAS) 及車載娛樂系統 (infotainment) 等車用 SoC 的 AEC-Q100 認證。這些組合可提供 ISO 26262 ASIL B / ASIL D Ready 的認證、AEC-Q100測試 (testing) 及 TS 16949 品質管理。與此同時,Galaxy 設計平台的數位 (digital)、客製 (custom) 及簽核 (signoff) 工具套件的也已通過認證。

此後,Synopsys Custom Compiler 解決方案可透過 iPDK 標準支援 TSMC 16FFC製程 PDKs,協助雙方共同客戶降低成本,並提升使用該製程進行設計的可靠度。隨著 FinFET 技術的拓展以及汽車設計應用功能日漸增加,設計的電流密度越來越高、有越來越多的線路易受到孔洞 (void) 及短路等 EM 效應影響。此外,FinFET 技術的溫度曲線會影響周遭金屬互連的溫度,即所謂的「自熱效應」(SHE),EM 失效機率亦隨之升高。為此,TSMC 強化電流模擬模型,以評估熱載子注入 (HCI) 及偏壓溫度不穩定性 (BTI) 等 SHE 對裝置可靠度機制所造成的影響。

Synopsys 最新版的 HSPICER、CustomSim 及 FineSimR 電流模擬器 (circuit simulators) 可協助設計人員針對電流效能衰退建立模型,有助於提升車用設計的可靠度。台灣新思總經理李明哲補充,即使 EDA、晶片設計和晶圓廠良率皆就緒,但軟體無法運作亦是枉然,唯有集結產業鏈各方力量加乘,才有實現整體優化的可能——因為「產品」才是最終的產出目標。他指出,台灣企業多為精實型,有利於 IoT 多量少樣發展;但產品開發完成後,需有軟體加持才能產生價值,實現 Smart Everything 或 Digital Intelligence。

深耕本地市場,創新研發不輟

李明哲宣示在台灣的四大發展策略:

1. 安身立命:自 2003 年開始擴大研發團隊、2012 年合併思源後,目前台灣已有超過 600 名員工,其中有 2/3 皆是工程人員;

2. 深耕本地:僱用員工幾乎皆是台灣本地人,配合政府的產業發展政策,Synopsys 自 2004 年即在台灣成立研發中心,不斷引進與推動創新設計軟體技術的研發,協助台灣半導體設計技術升級和先進設計解決方案研究;

3. 推動產業:Synopsys 相當肯定台灣 IC 畢業生皆有實作、試產晶片的能力,故決意從學校教育開始紥根,目前在台大、清大、交大、成大和中央大學皆設立「IoT 物聯網應用——前瞻設計實驗室」,另與工業局、資策會合作人才培訓計畫,作為學校教育及企業內訓補強,台灣新思科技近日更因此榮獲經濟部頒發「軟性價值夥伴獎」,是六年內三度受到肯定;

4. 成就用戶:台灣 IC 設計產業經過三十多年發展,在基礎教育、市場經營和競爭能力都有不錯表現,期能藉由引進全球思維,協助業者與國際接軌。

李明哲宣示在台灣的四大發展策略:

1. 安身立命:自 2003 年開始擴大研發團隊、2012 年合併思源後,目前台灣已有超過 600 名員工,其中有 2/3 皆是工程人員;

2. 深耕本地:僱用員工幾乎皆是台灣本地人,配合政府的產業發展政策,Synopsys 自 2004 年即在台灣成立研發中心,不斷引進與推動創新設計軟體技術的研發,協助台灣半導體設計技術升級和先進設計解決方案研究;

3. 推動產業:Synopsys 相當肯定台灣 IC 畢業生皆有實作、試產晶片的能力,故決意從學校教育開始紥根,目前在台大、清大、交大、成大和中央大學皆設立「IoT 物聯網應用——前瞻設計實驗室」,另與工業局、資策會合作人才培訓計畫,作為學校教育及企業內訓補強,台灣新思科技近日更因此榮獲經濟部頒發「軟性價值夥伴獎」,是六年內三度受到肯定;

4. 成就用戶:台灣 IC 設計產業經過三十多年發展,在基礎教育、市場經營和競爭能力都有不錯表現,期能藉由引進全球思維,協助業者與國際接軌。

照片人物:台灣新思 (Synopsys) 總經理李明哲

李明哲透露,已晋身為全球第十五大軟體公司的 Synopsys,擁有逾 4 億行的軟體編碼指令,其規模就連 Microsoft、Facebook 和 Google 都望塵莫及。李明哲指出,只要開放源碼,就有被駭或植入木馬的可能,另一個風險來自於版權。開發產品會涉及眾多智財和軟體,就算是免費使用、也可能有「授權」問題;但開發者可能因為不清楚採用元件或工具的內容而誤踩紅線,等到產品開發完成要上市時,才驚覺要被抽取相當高比例的授權費,根本毫無利潤、甚至血本無歸!Synopsys 認為,開放軟體除了考慮品質外,版權的追踪查核不可或缺。