7 奈米製程漸露曙光,加上近日傳出西門子 (Siemens) 將收購明導國際 (Mentor Graphics) 的消息,霎時吹皺 EDA (電子設計自動化) 產業一池春水。研調機構 Technavio 早先發佈報告指出,無晶圓廠半導體公司數量將持續上升,成為 EDA 市場的主要成長動力;預估 2016~2020 年 EDA 市場的年複合成長率 (CAGR) 約 8.52%。許多半導體公司基於聚焦設計及開發考量,轉而將半導體晶片製造、測試和組裝委外代工,往無晶圓業務結構推進;預估未來全球專業代工廠和無晶圓廠半導體公司最終比例將達 1:11。

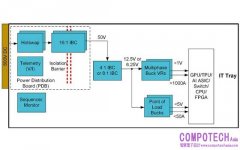

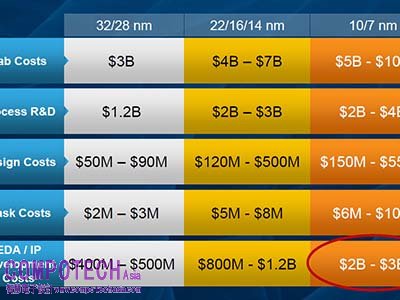

圖1:半導體產業在奈米製程的投資概況 (單位:美元)

資料來源:IBS;Cadence

亞洲成長驚人,IoT 或成下波動力

值得關注的是,亞洲因 OEM 廠商盛行加上承包全球軟體開發工作之故,亞太區成長力道尤為驚人,而高階研究及開發投資將是市場的關鍵驅動來源。Technavio 統整對 EDA 市場最具貢獻度的四大元素為:

1. 系統單晶片 (SoC) 技術需求上揚:智能器具及數位家庭市場歷經十多年發展,導致終端市場對高功率、效率和智能電子裝置需求日增,如何借助高階製程將數以幾十億計的電晶體整合在一個特定晶片上、實現嵌入式圖像和多核心技術與晶片設計複雜度亦隨之升高;在無線通訊設備、心電圖 (ECG)、智慧手機、遙測 (telemetry) 和汽車電子等領域已開始採用 SoC,而系統級封裝、混合訊號 SoC 製造商也有能力以「中價位」提供整合更多功能的單晶片。

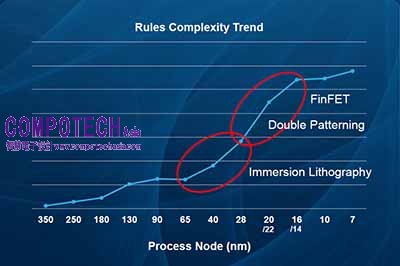

2. 電子裝置微型化需要跨域的精準度支撐:輕薄短小不再是消費類市場專利,通訊、汽車、工業和醫療保健設備亦希望電子器件的尺寸能盡量壓縮,促使 IC 製造商增加研發支出以求晶片效能最佳化,讓微機電 (MEMS) 和 3D 半導體順勢興起;由於必須在有限空間中增加互連元件和電晶體數目,晶圓沈積 (deposition) 和蝕刻圖樣 (patterning) 亦需更加細緻化。

3. 鰭式場效電晶體 (FinFET) 架構獲採用:因應物聯網 (IoT) 環境,消費類電子為改善效能並減少功耗,製程從平面的場效電晶體 (FET) 演進至立體 FinFET,預估可提升 37% 效能並減少 50% 以上的動態功耗或高達 90% 的靜態洩露電流;如此繁複的性質與介電質蝕刻 (dielectric etching) 息息相關,須從 IC 設計階段就納入考慮,慎始慎終。

4. 高度研發投資:半導體產業 2015 年的研發支出達 564 美元,不過,這個數字與前期相比只成長 0.5%,不僅遠遠落後於 2010 年以來 13% 的平均成長率、以及 2005~2015 年 4% 的年平均複合成長率 (CAGR) 水準,且創下 2009 年以來最低記錄;全球性的經濟放緩可能迫使廠商削減研發支出,包括新興技術費用。

值得關注的是,亞洲因 OEM 廠商盛行加上承包全球軟體開發工作之故,亞太區成長力道尤為驚人,而高階研究及開發投資將是市場的關鍵驅動來源。Technavio 統整對 EDA 市場最具貢獻度的四大元素為:

1. 系統單晶片 (SoC) 技術需求上揚:智能器具及數位家庭市場歷經十多年發展,導致終端市場對高功率、效率和智能電子裝置需求日增,如何借助高階製程將數以幾十億計的電晶體整合在一個特定晶片上、實現嵌入式圖像和多核心技術與晶片設計複雜度亦隨之升高;在無線通訊設備、心電圖 (ECG)、智慧手機、遙測 (telemetry) 和汽車電子等領域已開始採用 SoC,而系統級封裝、混合訊號 SoC 製造商也有能力以「中價位」提供整合更多功能的單晶片。

2. 電子裝置微型化需要跨域的精準度支撐:輕薄短小不再是消費類市場專利,通訊、汽車、工業和醫療保健設備亦希望電子器件的尺寸能盡量壓縮,促使 IC 製造商增加研發支出以求晶片效能最佳化,讓微機電 (MEMS) 和 3D 半導體順勢興起;由於必須在有限空間中增加互連元件和電晶體數目,晶圓沈積 (deposition) 和蝕刻圖樣 (patterning) 亦需更加細緻化。

3. 鰭式場效電晶體 (FinFET) 架構獲採用:因應物聯網 (IoT) 環境,消費類電子為改善效能並減少功耗,製程從平面的場效電晶體 (FET) 演進至立體 FinFET,預估可提升 37% 效能並減少 50% 以上的動態功耗或高達 90% 的靜態洩露電流;如此繁複的性質與介電質蝕刻 (dielectric etching) 息息相關,須從 IC 設計階段就納入考慮,慎始慎終。

4. 高度研發投資:半導體產業 2015 年的研發支出達 564 美元,不過,這個數字與前期相比只成長 0.5%,不僅遠遠落後於 2010 年以來 13% 的平均成長率、以及 2005~2015 年 4% 的年平均複合成長率 (CAGR) 水準,且創下 2009 年以來最低記錄;全球性的經濟放緩可能迫使廠商削減研發支出,包括新興技術費用。

圖2:設計複雜度會隨著製程節點微縮趨於複雜,65 nm 以下製程難度更形陡峭

資料來源:Cadence

看準 IoT 商機,EDA 領導廠商之一的益華電腦 (Cadence) 在今年「CDNLive使用者大會」中,特邀集多家科技大廠來分享 EDA 與物聯網所碰撞的火花。聯發科技設計技術研發本部總經理黃世安表示,智慧手機成長雖有趨緩之勢,但仍是發展 IoT 的良好平台和樞紐 (Hub)。為增加運算能力,現有手機架構必須有所改變;藉由 EDA 工具引進模型,可快速製作原型並掌握使用情境,方便與客戶溝通,對硬體架構設計的取捨亦更加進退有據。廣達電腦技術長暨副總經理張嘉淵從另一角度觀察:以手機作為中介平台,須留意平衡區域端運算的問題。

物聯網方興未艾,EDA 協助縮短開發時程

張嘉淵表示,IoT 嚴格來說並非新概念,早先之所以未倏然雀起,主要是「應用」未到位。然而,是否能把這麼多的通訊功能整合到一個低功耗的小裝置?或是沿用手機作為使用中樞?牽動的不僅是單一產品,而是整個生態系。廣達認為,為每一個連網裝置個別優化,降低手機接收、處理從各裝置產生大量數據的負載,不失為另一種可行方式。他並以易經中的一句話:「群龍無首,吉」,勉勵有志參與 IoT 盛會的企業,好好把握此一百花齊放的契機;因為這意謂新一輪競賽的大局未定、勝負未分,各路英雄還有很大的拼搏空間。

張嘉淵表示,IoT 嚴格來說並非新概念,早先之所以未倏然雀起,主要是「應用」未到位。然而,是否能把這麼多的通訊功能整合到一個低功耗的小裝置?或是沿用手機作為使用中樞?牽動的不僅是單一產品,而是整個生態系。廣達認為,為每一個連網裝置個別優化,降低手機接收、處理從各裝置產生大量數據的負載,不失為另一種可行方式。他並以易經中的一句話:「群龍無首,吉」,勉勵有志參與 IoT 盛會的企業,好好把握此一百花齊放的契機;因為這意謂新一輪競賽的大局未定、勝負未分,各路英雄還有很大的拼搏空間。

照片人物:(左起) 智原科技資深處長王志恆、Cadence 全球副總裁暨亞太區總裁石豐瑜、Cadence EDA 策略長暨資深副總裁徐季平、

廣達電腦技術長暨副總經理張嘉淵、Cadence 台灣區總經理宋栢安

矽智財 (SIP) 供應商智原科技則為 Cadence 見證說:透過結合其階層式方法與分割指引 (partition guideline),可將 3 億個邏輯閘數的複雜晶片設計原型之每次產出分析時程,從兩星期大幅縮短至 3~5天,在七個月內完成開發。資深處長王志恆表示,現在 IC 整合越來越多的功能,不可能所有的 IP 研發都自己來,對 IP 授權有一定的需求;而 IP 又涉及驗證問題,EDA 廠商也積極經由併購或策略合作,在 IP 領域投注相當多心力;「說不定未來也有自己跳下來賣 IP 的可能」,他打趣地說。在跨界「大亂鬥」的物聯網時代,EDA 未來之路將更為寬廣。