2016年12月7日--球領先的奈米電子及數位技術研發與創新中心比利時微電子研究中心,在本週的 IEEE IEDM 研討會上首度展示鈍化矽鍺 nMOS匣極堆疊,介面缺陷密度(DIT)大幅降低至與矽匣極堆疊相同的等級,並且具有極高的電子遷移率與較低的正向偏壓溫度不穩定性(PBTI)。這些具前瞻性的成果,為鍺基鰭式電晶體與匣極全環繞元件奠定良好的基礎,為 5nm 級以上的邏輯元件提供許多可能性。

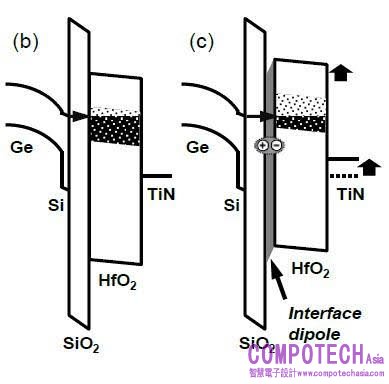

現今的成果是藉由應用能帶工程所取得,在高 k 值/二氧化矽介面上採用介面電偶極,並且採取氫高壓退火(HPA)作為製程的結尾。藉由進行原子層沉澱(ALD)這項 3D 相容製程來沉澱矽酸鑭層,二氧化矽層上便會形成介面電偶極。雖然高 DIT 向來是鈍化矽鍺 nFET 的一項主要疑慮,但這個問題已藉由插入矽酸鑭與採用氫高壓退火技術來大幅降低 DIT,並首度在中間能隙附近從 2x1012 cm-2eV-1 降至 5x1010 cm-2eV-1。採用以上技術後,電子遷移率便因此得以提升(在峰值處約為百分之 50);而由於能帶工程中引入介面電偶極,PBTI 的可靠度因此而獲得提升。

在 IEEE IEDM 上,比利時微電子研究中心也展示了高雜質半導體的異質結構介面電阻(Rhi)之分析模型。比利時微電子研究中心已採用這項創新的模型,對 TiSix/Si:P/n-Ge 接觸堆疊中的高雜質 Si:P 進行預測,以幫助克服鍺 nMOS 中的高接觸電阻問題。隨著開發出先進的低溫 Si:P 磊晶技術,比利時微電子研究中心展現了創下紀錄的 TiSix/Si:P/n-Ge 接觸堆疊之 n-Ge 低接觸電阻。

「我們致力於拓展摩爾定律的極限,在相關的研究中,鍺基元件便是其中的關鍵。」半導體技術與系統部門執行副總裁 An Steegen 表示。「這些突破性的成就,在為了讓鍺基元件成為 5nm 以上等級之可行解決方案所努力的過程中,我們對於瞭解需要克服的基本阻礙所投入的心力,寫下了重要的篇章。」

這項成果是與 ASM、Poongsan 以及南洋理工大學協力執行的成果。比利時微電子研究中心對先進邏輯縮放技術的研究,是與比利時微電子研究中心的核心 CMOS 計畫之關鍵合作夥伴一起進行,其中包含格羅方德、華為、Intel、美光、高通、三星、SK 海力士、Sony 以及台積電。

本新聞稿可於以下網址下載 http://www2.imec.be/be_en/press/imec-news/imec-IEDM-Ge-nMOS-devices.html

能帶圖:沒有介面電偶極的鈍化矽鍺 nFET (b) 以及高 k 值/二氧化矽介面處的介面電偶極

藉由插入矽酸鑭與採取 HPA後獲得改善的鈍化矽鍺匣極堆疊之 DIT示意圖

關於比利時微電子研究中心

比利時微電子研究中心在奈米電子與數位科技領域為世界頂尖的研究與創新先驅。我們在微晶片科技備受稱譽的領先地位,以及軟體與資訊與通訊科技的專長,讓我們脫穎而出。透過世界一流的基礎設施,以及在地與全球生態系中各領域夥伴的協助,我們得以在醫療、智慧城市與智慧行動、物流與製造和能源等領域進行突破與創新。

比利時微電子研究中心是許多企業、新創公司與大學信任的合作夥伴,並網羅來自世界各地 70 個國家/地區、近 3,500 位的優秀人才。比利時微電子研究中心總部設立於比利時魯汶,並於多所法蘭德斯區大學、荷蘭、台灣、美國、中國等地設有研發團隊,而在印度與日本設有辦公室。比利時微電子研究中心於 2015 年度的營收(根據損益表)總額為 4.15 億歐元,而於 2016 年 9 月 21 日納入旗下的 iMinds 也創下 5,200 萬歐元的營收。如需更多資訊,歡迎造訪官方網站:www.imec.be

比利時微電子研究中心(Imec)是 IMEC International(根據比利時法律設立為「公益基金會」之法律實體)、imec Belgium(獲得法蘭德斯政府支持的 IMEC 非營利組織)、imec the Netherlands((IMEC Nederland 基金會,屬於Holst Centre的一部分,並受到荷蘭政府支持)、imec Taiwan(台灣愛美科股份有限公司)、imec China(IMEC 微電子(上海)有限公司)、imec India(IMEC 印度私人有限公司)及 imec Florida(IMEC 美國奈米電子設計中心)旗下活動使用之註冊商標。