2018年3月19日--美商賽靈思(NASDAQ: XLNX)為自行調適與智慧運算的領導廠商,今日發表一款突破性新型產品,名為ACAP(Adaptive Compute Acceleration Platform,自行調適運算加速平台),其功能大幅超越FPGA的極限。ACAP為一個超高整合度的多核心異質運算平台,能針對各種應用與工作負載需求,從硬體層面進行靈活變化。 ACAP能在運行過程中動態調整的自行調適能力,提供CPU與GPU無法比擬的效能和效能功耗比。

在巨量資料與人工智慧正興起的時代,ACAP非常適用於加速廣泛的各種應用,其中包括視訊轉碼、資料庫、資料壓縮、搜尋、人工智慧推論、基因組、機器視覺、運算儲存以及網路加速等。軟硬體開發人員能針對端點、邊緣及雲端等應用著手開發搭載基於ACAP的產品。代號為「Everest」的產品是首款採用台積公司7奈米製程技術的ACAP產品系列,預計於今年年底投產。

圖一:賽靈思發表一款名為ACAP的突破性新型產品

賽靈思總裁暨執行長Victor Peng表示:「這不僅是顛覆業界的重大技術,更是自發明FPGA以來最重要的工程成就。此革命性的全新架構是賽靈思擴大市場策略的一部份,將幫助公司朝FPGA以外的領域發展,並突破『僅支援硬體開發者』的侷限。ACAP產品在資料中心與廣大市場的運用,將加速自行調適運算的普及化,進而加快實現智慧、聯網、自行調適的世界願景。」

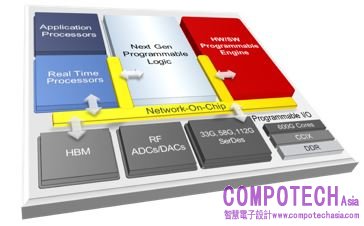

圖二:今日宣布的ACAP與「Everest」行動為賽靈思未來願景的一部分

ACAP 技術細節

在ACAP核心內有個全新世代的FPGA架構,其結合分散式記憶體與硬體可編程DSP模塊、一顆多核心SoC,以及一個或多個軟體可編程且硬體自行調適的運算引擎,上述元件皆透過網路晶片(NoC)串連。此外,ACAP具高度整合的可編程I/O功能,依據不同元件類型,其功能涵蓋整合的硬體可編程記憶體控制器、先進的串列器技術、具領導地位的邊緣RF-ADC/DAC,到整合的高階頻寬記憶體(HBM)。

在ACAP核心內有個全新世代的FPGA架構,其結合分散式記憶體與硬體可編程DSP模塊、一顆多核心SoC,以及一個或多個軟體可編程且硬體自行調適的運算引擎,上述元件皆透過網路晶片(NoC)串連。此外,ACAP具高度整合的可編程I/O功能,依據不同元件類型,其功能涵蓋整合的硬體可編程記憶體控制器、先進的串列器技術、具領導地位的邊緣RF-ADC/DAC,到整合的高階頻寬記憶體(HBM)。

軟體開發者能運用包括C/C++、OpenCL及Python等語言,來搭載基於ACAP的系統。此外,ACAP還可運用FPGA工具,從RTL層進行編程。

市場調查研究公司Moor Insights & Strategy 創辦人Patrick Moorhead表示:「這就是未來運算的形式,我們所談的是能在幾分鐘內做到基因組定序,而不是幾天;或是像資料中心能依據運算需求自行編程伺服器來調整工作負載,例如白天進行視訊轉碼,而晚上進行影像辨識。此點意義非凡!」

ACAP歷經四年的研發,其累積投入的研發費用超過十億美元。賽靈思目前有超過1,500位軟硬體工程師負責設計「ACAP與Everest」,且相關軟體工具已提供予重要客戶。「Everest」將於今年投產,並預計於2019年出貨。

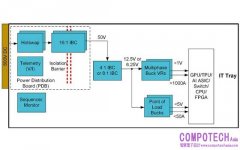

圖三:Everest行動

「EVEREST」提升效能

以現今最新16奈米Virtex® VU9P FPGA為基準,「Everest」在執行深度神經網路的運算時,預計將提升高達20倍的效能;而以「Everest」為基礎的5G遠端無線電頭端設備,則將提供比目前最新16奈米無線電元件多4倍的頻寬;屆時,汽車、工業、科學、醫療、航太與國防、測試/測量與模擬、影音與廣播,及消費電子市場等廣泛的應用,都將獲得大幅的效能提升及更高的功率效益。

以現今最新16奈米Virtex® VU9P FPGA為基準,「Everest」在執行深度神經網路的運算時,預計將提升高達20倍的效能;而以「Everest」為基礎的5G遠端無線電頭端設備,則將提供比目前最新16奈米無線電元件多4倍的頻寬;屆時,汽車、工業、科學、醫療、航太與國防、測試/測量與模擬、影音與廣播,及消費電子市場等廣泛的應用,都將獲得大幅的效能提升及更高的功率效益。

圖四:ACAP技術

今日宣布的ACAP與「Everest」行動,是Peng對賽靈思未來願景的一部分(詳情請參考:新聞稿)。欲知更多訊息,敬請瀏覽賽靈思官網www.xilinx.com,或追蹤賽靈思Twitter:@XilinxInc、Facebook:facebook.com/XilinxInc或LinkedIn:linkedin.com/

company/Xilinx。

關於賽靈思

賽靈思公司(Xilinx, Inc.;NASDAQ:XLNX)致力於發展高度彈性與自行調適的處理平台,為用戶從端點到邊緣再到雲端的眾多技術領域中,提供快速創新的支援。賽靈思為FPGA、硬體可編程SoC及ACAP的發明者,旨在為業界提供最具動能的處理器技術,實現自行調適、智慧互聯的未來世界。欲瞭解更多資訊,請瀏覽www.xilinx.com網站。