imec提出3D電荷耦合元件結合IGZO通道 作為資料密集運算應用的緩衝記憶體

前言:

全新的開放式高速互連協定CXL Type 3緩衝記憶體有望大幅超越動態隨機存取記憶體(DRAM)的位元密度和成本效率。

2024年12月12日--於本周舉行的2024年IEEE國際電子會議(IEDM)上,比利時微電子研究中心(imec)提出一款創新的3D整合電荷耦合元件(CCD),可作為一種記憶區塊可定址的緩衝記憶體來運作,支援資料密集的運算應用。該記憶體的運作在平面式CCD的概念驗證架構上展示,具備142位元的儲存能力。採用氧化物半導體通道材料(例如氧化銦鎵鋅)的做法不僅確保資料保存時間夠長,也能在符合成本效率和類似於3D NAND的架構實現3D整合。imec預期這種3D CCD的記憶體密度會增加,遠遠超越動態隨機存取記憶體(DRAM)的極限。

開放式高速互連協定CXL記憶體介面於近期推出,為新型記憶體提供發展機會,使其在人工智慧(AI)和機器學習(ML)等資料密集運算應用輔助DRAM。CXL Type 3緩衝記憶體是其中一例,該記憶體預計會用作一種外接記憶體池,藉由一顆高頻寬的CXL交換器來把大型的資料區塊「饋入」各種處理器核心。這類記憶體所採用的規格不同於以位元組(byte)為定址單位的DRAM,後者越來越難以維持每位元成本的微縮趨向線。

於2024年IEEE國際電子會議(IEDM),imec提出一款包含氧化銦鎵鋅(IGZO)的電荷耦合元件(CCD),採用3D NAND快閃記憶體的串列結構進行整合,作為有潛力發展為CXL Type 3緩衝記憶體的候選技術—目標是實現記憶區塊可定址、無限重複讀寫、低製造成本和充分資料保留時間這些所需的特性。

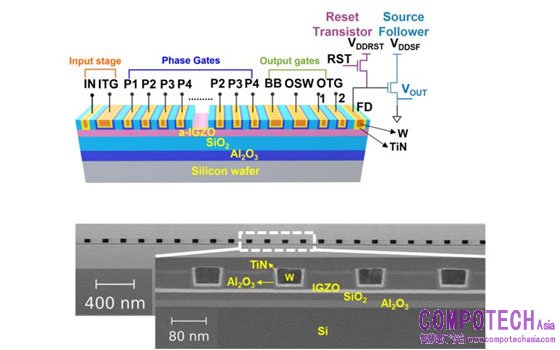

imec為實際應用所採取的第一步是在2D概念驗證展示了這款包含IGZO材料的CCD記憶體運作。此2D概念驗證的平面式CCD結構包含1個輸入級、142個階段(每階段包含四相閘極且可儲存1位元)以及1個雙電晶體型讀取級。CCD暫存器的資料寫入是透過輸入級來注入電荷,隨後經由所有142個階段來傳輸電荷—藉由切換相位閘極的電壓來實現。該CCD元件提供超過200秒的資料保留時間、至少1010 次的耐久性且毫無衰退,以及超過6MHz的電荷傳輸速度。CCD暫存器的多階儲存能力也經過證明,能有助於提高位元密度。以電荷為基礎的CCD技術獲得影像感測器市場的廣泛採用,具備知名度、可靠度和低電壓的運作能力—帶來功耗方面的優勢。

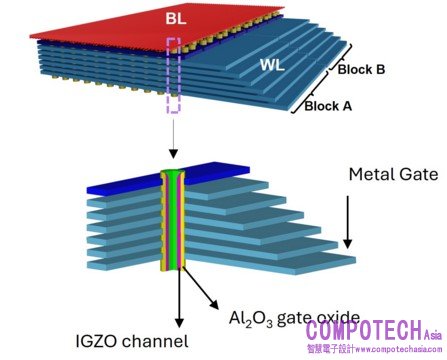

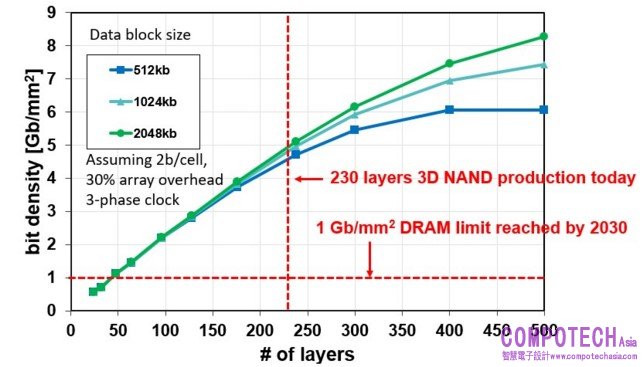

imec儲存記憶體研究計畫主持人Maarten Rosmeulen表示:「imec提出的這種緩衝記憶體,其真正價值在於利用3D NAND的方式進行整合的能力,包含基於IGZO並整合於垂直對齊的插孔內的CCD暫存器—我們目前首度提出的概念。就目前可能實現的NAND快閃記憶體來說(即230層的堆疊能力),我們預估,我們的3D緩衝記憶體已經能提供比(2D)DRAM在2030年內預計達到的位元密度還要增加5倍。我們現在正利用有限的字元線來研究實際的3D技術應用。」

圖一:(上圖)基於氧化銦鎵鋅(IGZO)的平面式CCD結構示意圖,以及(下圖)一系列閘極的穿透電子顯微鏡(TEM)截面圖,包含各元件層的細部特寫。

圖二:(上圖)此次提出的3D整合且基於IGZO之CCD記憶體區塊,包含設置在垂直對齊插孔和字元線(WL)內的整合式CCD暫存器,將其用為CCD閘極;(下圖)單顆CCD暫存器的截面特寫,顯示一串IGZO金屬氧化物半導體(MOS)電容器。

圖三:比較預測位元密度與所提出的3D CCD記憶體層數,假設每記憶體單元為2位元,陣列使用損失率為30%,且以三相時脈運作。

比利時微電子研究中心(imec)簡介

比利時微電子研究中心(imec)是在奈米電子與數位科技領域中領先世界的研究與創新中心。憑藉先進研發設備以及5500多名員工和頂尖研究人員組成的團隊,imec的研究技術包括先進半導體和系統微縮技術、矽光子、人工智慧、超5G通信和感測技術,並延伸其他領域的應用, 如健康與生命科學、交通運輸、工業4.0、農糧產業、智慧城市、永續能源、教育等應用領域。 imec結合了整個半導體核心價值鏈中的先行者、以佛蘭德斯為根基加上國際級科技、製藥、醫療和ICT公司,新創產業以及學術機構和研究中心。imec的總部位於比利時魯汶,在比利時、荷蘭、英國和美國設有研究機構,並在三個大洲設有辦事處。2023年,imec的收益(損益表)總計9.41億歐元。

有關比利時微電子研究中心(imec)的更多訊息,請到官網www.imec-int.com。