自從台積電公開宣稱「物聯網是 The Next Big Thing」後,三年來,IoT 究竟與半導體產業碰撞出怎樣的火花?是否引發某些質變?位居半導體最上游的新思科技 (Synopsys) 有著深切體會。Synopsys 董事長暨共同執行長 Aart de Geus 重申:物聯網的核心精神及終極目標在於「Smart Everything」。在言必及 IoT 的今天,為讓產品及服務持續 Smarter、Smartest 以強化市場競爭力,業界往往須設法在有限的晶片集成更多電路、在電路板上整合更多連網功能,另一方面,又要盡力滿足低功耗需求;因此,很多設計細節必須從源頭就納入考量,不宜各行其是。

照片人物:Synopsys 董事長暨共同執行長 Aart de Geus

Aart de Geus 觀察到,「機器學習」(Machine Learning) 在穿戴式裝置、醫療、智慧家庭/城市、汽車、工業自動化及金融等應用越來越廣,如何完美融合軟、硬體與演算法將是最根本的專業知識;例如,欲建置車聯網 (V2X) 環境,需要多少攝影機、距離多遠煞停?「軟、硬體的同步開發很重要,可提前磨合、及時發現錯誤並修正,否則容易導致後續接手或整合者不知所措或誤入歧途」,他強調。此外,萃取出各個工作環節的共通性並加以「實體化」(physical)——例如:借助經過融合、匯整的感測資料或驗證的演算法,優化最終結果、提升預測價值。

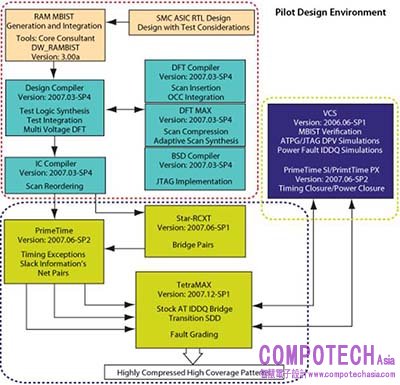

從概念發想、原型設計及製作、試產到正式量產變數極多,每一步皆須步步為營,最怕的就是不確定眼下這個動作是否能獲得符合預期的回饋?若有異常,如何避免一錯再錯、以致積重難返?於是,可測性設計 (DFT) 和可製造性設計 (DFM) 顯得不可或缺。前者在設計初始就將移位暫存器等俗稱「掃描鏈」的技術植入電路,讓測試人員得以從外部控制並觀測電路內部觸發器的訊號值,可省卻諸多測試調校及變更設計往返的麻煩;後者著重與生產線部門及各方利益關係人 (包括外部上、下游的供應商與客戶) 的協同工程,有助消弭歧見、加速開發專案時程。

圖1:Synopsys DFT 導入流程 資料來源:Synopsys 官網

所謂「行百里者半九十」,即使整體開發工程已九成達標,只要未順利產出,都有前功盡棄的風險。DFM 旨在研究產品本身的物理特徵與製造系統的相互關係,並將其回溯至前端設計予以標準化、簡單化,更利於生產及使用、提高工作效率、降低成本。以上種種,皆是敦促半導體不斷往前邁進的動力。Aart de Geus 指出,摩爾定律闡述的是「增加 IC 電晶體數目可提升晶片效能」,加上類比、數位混合設計及各式演算法的與日俱增,這意味著邏輯閘的複雜度將大幅攀升;為促進不同工作環節順利銜接或協作,電子設計自動化 (EDA) 將發揮關鍵效益。

早在 1980 年代後期,Synopsys 就投入數位模擬及建模合成工程,之後更致力於高品質智財專利的重覆使用性 (IP reuse) 及軟、硬體開發,尤其重視軟體安全;為協助用戶提供更好的產出品質 (QoR)、更短的測試時間 (TTR) 及更低廉的產出成本 (CoR),目前更加快發展機器學習及平台融合的腳

步。「我們擁有經年累月蓄積而成的大數據做支撐,包括半導體材料和參考流程的演變,可因應晶片設計日趨升高的複雜度,是我們在機器學習的先天優勢,也是作為 IoT 引擎深厚的資本」,Aart de Geus 具體說明 Synopsys 在物聯網時代的超凡定位與策略藍圖。

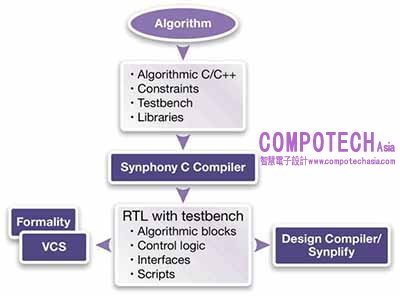

圖2:Synopsys 的「Synphony C 編譯器」支援C / C ++ 合成、模擬和除錯

資料來源:Synopsys 官網