新思科技與台積公司攜手讓具有數兆個電晶體的AI與多晶粒晶片設計 成為可能

前言:

優化的電子設計自動化與IP解決方案為台積公司的N2與A16製程

提供更高的運算效能、功耗與工程生產力

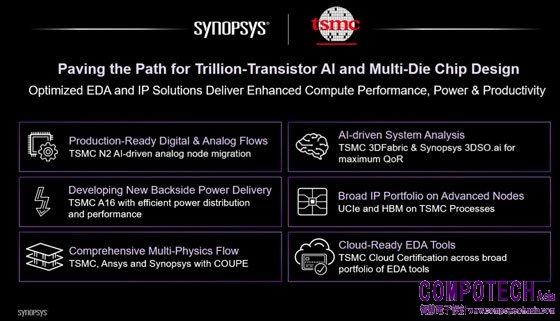

新思科技近日宣布持續與台積公司密切合作,並利用台積公司最先進的製程與3DFabric技術提供先進的電子設計自動化 (EDA)與IP解決方案,為AI與多晶粒設計加速創新。由於AI應用對運算的需求永不停歇,半導體產業需要跟上步伐。從透過Synopsys.ai™ 提供支援以提升生產力與矽晶片結果,領先業界的AI驅動EDA套裝軟體,到促成往2.5D/3D多晶粒架構遷移的完整解決方案,新思科技與台積公司已經密切合作數十年,為未來包含數十億個到數兆個電晶體的AI晶片設計,創造出良好的條件。

台積公司生態系統與聯盟管理主管Dan Kochpatcharin表示:「台積公司很高興能與新思科技合作,利用台積公司先進的製程與3DFabric技術,為AI設計嚴苛的運算需求量身訂做並開發具開創性的EDA與IP解決方案。」他說:「我們最近與新思科技的各種AI驅動EDA套件及通過矽認證(silicon-proven)的IP協作取得的成果,協助我們共同的客戶大幅提升生產力,並為先進AI晶片的設計在效能、功耗與面積上帶來顯著的成果。」

新思科技EDA產品管理資深副總裁Sanjay Bali表示:「數十年來,新思科技持續與台積公司密切合作,為橫跨所有世代的台積公司最先進節點,提供必須的EDA與IP解決方案。」他指出:「對於協助我們共同的客戶在AI年代加速創新並推進半導體設計的未來,此一合作夥伴關係扮演著舉足輕重的角色。我們正共同挑戰科技可能性的極限,並在效能、功耗效率與工程生產力方面,促成具有開創性的進展。」

新思科技AI驅動的EDA設計流程大幅推進效能、功耗與面積效率與工程生產力

領先業界的企業已欣然採用新思科技以AI驅動的EDA流程,藉由Synopsys.ai提供支援,用於N2製程上的先進晶片設計。

聯發科公司副總經理吳慶杉表示:「新思科技通過認證的客製化設計解決方案Custom Compiler與PrimeSim,在效能與生產力方面提供的助益,讓我們的設計人員得以在台積公司的N2製程上,滿足高效能類比設計的矽晶片需求。」他說:「我們與新思科技擴大協作,讓我們得以充份發揮他們以AI驅動流程的潛力、加速我們在設計遷移與優化方面的努力,並提升我們將領先業界的系統單晶片導入各垂直市場所需的流程。」

此外,新思科技也與台積公司針對全新的晶背(backside)繞線功能展開協作,並在新思科技的數位設計流程中支援台積公司的A16製程,以應對配電與訊號繞線的需求,達成設計上效能效率與密度的優化。新思科技也提供設計團隊可相互操作的製程設計套件(iPDKs)以及Synopsys IC Validator™實體驗證程序執行檔(runset),以應付實體驗證規定與日俱增的複雜性,並以高效率把設計轉換到台積公司的N2製程技術。

為了進一步加速晶片設計,新思科技與台積公司透過台積公司的雲端認證在雲端啟用新思科技的EDA工具,提供共同客戶雲端就緒的EDA工具、帶來精準的結果品質,並能與台積公司先進的製程技術無縫整合。新思科技通過雲端認證的工具,包括電路合成、佈局與繞線、靜態時序與功耗分析、電晶體層級靜態時序分析、客製化實作、電路模擬、EMIR分析,以及設計規則檢查。

利用完整的EDA解決方案推進多晶粒的創新

新思科技、Ansys及台積公司彼此合作,借助於三方主要的解決方案,透過全面的系統分析流程,解決多晶粒設計複雜的多物理場挑戰。這個基於Synopsys 3DIC Compiler從探索到簽核平台一元化的最新流程,整合3DSO.ai並結合供數位與3D積體電路使用的Ansys RedHawk-SC™功耗完整性簽核平台,提升溫度與壓變感知的時序分析。新思科技的3DIC Compiler是一個已經取得台積公司認證的平台,它支援3Dblox與涵蓋TSMC-SoIC® 與CoWoS封裝技術的3DFabric。

Ansys公司半導體、電子暨光學事業群副總裁兼總經理John Lee表示:「我們與新思科技及台積公司的合作,是我們對驅動創新、促成AI未來與多晶粒晶片設計共同承諾的典範。」他指出:「我們齊心協力一起應對多晶粒架構固有的多重物理量挑戰,並協助我們的共同客戶利用台積公司最新的技術,於新思科技的設計環境中,在晶片、封裝與系統層級達成絕佳的簽核精確度效果。」

利用通過矽認證的IP降低風險

新思科技全面的多晶粒測試解決方案可與Synopsys UCIe 與HBM3 IP一起使用,可以確保製造測試與現場運作期間多晶粒封裝的健康狀況。新思科技攜手台積公司,已使用台積公司的CoWoS中介層技術實際投片出測試晶片,全面支援測試、監控、除錯與修復功能。其診斷、可追溯性與任務模式的訊號完整性監控,可以針對諸如預測性維護等目的,達成設計中(in-design)、拉升改善中(in-ramp)、生產中(in-production)及現場(in-field)的優化。UCIe PHY的監控、測試與修復(MTR) IP,提供晶粒、晶粒到晶粒介面與多晶粒封裝層級,的可測試性。

新思科技在N3E與N5等製程技術的UCIe 和HBM3 IP解決方案,取得多項矽晶成功案例,加速IP整合並把風險降至最低。最新開發的Synopsys UCIe IP運作速率高達40G,毋需額外的面積即可實現最大的頻寬與最高的能源效率;至於HBM4 與3DIO IP解決方案則在台積公司的先進製程上,加速3D堆疊晶粒的異質整合。

更多資源

• Linkedin文章:新思科技與台積公司藉由台積公司的CoWos技術,成功實際投片出具備多晶粒設計特色的測試晶片

關於新思科技(Synopsys, Inc.)

新思科技(Synopsys, Inc.) 為推動普世智慧時代的到來,提供值得信賴且全面的晶片到系統設計解決方案,含括電子設計自動化(EDA)到晶片 IP 以及系統驗證等。我們與各行各業的半導體和系統客戶密切合作,協助客戶大幅提高研發能力和生產力;致力於推動今日的創新,點燃明日的創造力。 瞭解更多信息,更多詳情請造訪 www.synopsys.com。

本月熱點 HOME

- 賀天銘(Benjamin Hein)將於 2026 年

- 是德科技以高功率與百萬瓦級充電

- Palo Alto Networks 完成收購 Chronospher

- 三星率先出貨業界首款商用HBM4 為

- 降低嵌入式系統 RAM 使用量,以壓低

- 跨鏈科技攜手 Liminal 強化台灣合規

- QuiX Quantum與Artilux光程研創進行策略

- Ceva Wi-Fi 6 和藍牙 IP 為瑞薩電子首款

- 達梭系統3DEXPERIENCE World 2026 人工智

- Anritsu 安立知領先推出支援 6G FR3 頻

- Palo Alto Networks 完成收購 CyberArk,

- 晶泰科技自動化實驗室落地巴斯夫