在 RF 接收器中,透過基準時脈緩衝和分配引入的時脈抖動可能限制可實現的系統性能。為了獲得寬鬆的前端濾波器要求而採用相對較高的中頻 (IF) 時,對低抖動的要求會進一步提高。本文詳細探討了 325MHz IF 取樣系統的設計,並提出了將正弦波基準訊號轉換為一對差動 LVPECL 時脈的時脈緩衝器和分配器,該時脈緩衝器和分配器適用於驅動高速 ADC,而且驅動高速 ADC 時,可將所引入的抖動降至最小。

系統描述

在 IF 取樣 (或欠取樣) 系統中,ADC 完成 RF 接收器中最後一級下變頻。IF 越高,RF 前端的鏡頻抑制濾波器的陡度就越小,這有助於減小濾波器的成本、尺寸和插入損耗,並進一步減少對放大的需求,但也反過來會導致更低的成本和功耗。圖 1 所示為一個典型和採用 IF 取樣的 RF 接收器鏈路。

圖 1:典型單 IF 級 RF 接收器方塊圖

設計接收器時,採用相對較高 IF的缺點,是在對較高頻率的類比輸入訊號取樣時,系統性能規格更容易受到 ADC 性能降低的影響。例如,在輸入頻率較高時,ADC 的無寄生動態範圍 (SFDR) 變差了。更重要的是,在對更快速的輸入取樣時,ADC 的孔徑抖動和時脈抖動相結合,限定了可實現的訊號雜訊比 (SNR)。

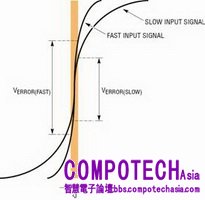

時脈抖動的影響可以透過比較由於時脈抖動所引起的電壓誤差值、同時採用相同的 ADC 和時脈對兩個擺動訊號 (其中一個訊號的斜率高於另一個訊號) 進行取樣來展示。該時脈具有相同的時間抖動量 (tJ的單位為 s-RMS),並按圖 2 所示對兩個訊號實施取樣。對於移動速度較快的訊號,因時脈抖動而引起的不確定性確實較高,因此,當類比輸入具有較高的頻率分量時,時脈抖動是一個限制 SNR 指標的主要 (如果不是主導的話) 誤差源。所以,盡可能地抑制 ADC 時脈 (在圖 1中表示為 IF 取樣時脈) 的抖動是最重要的。

圖 2:在對緩慢和快速擺動訊號進行數位化處理的過程中時脈抖動所造成的影響

為了避免在 ADC 時脈輸入端上發生 AM 至 PM 雜訊轉換,該時脈應具有一個高的擺率,理想情況下是一個方波。ADC 的時脈輸入產生一個限幅器的作用,其獲取一個訊號並透過在輸入訊號的零 (或某些其他的基準) 交叉點上做出決策來對此訊號進行方波處理。當輸入訊號具有一個緩慢的擺率時 (比如在一個低頻和/或低幅正弦波中,與方波相比,訊號透過零交叉點類似於慢動作),將發生 AM 至 PM 雜訊轉換。假如存在任何類型的 AM 雜訊 (例如:電阻器熱雜訊,來自於電源的耦合雜訊等),則輸入訊號的零交叉點在隨後的脈衝邊緣之間變得不一致,從而導致在限幅器的輸出端上產生抖動;於是,AM 雜訊轉換為 PM 雜訊。反之,倘若輸入訊號快速透過零交叉點 (比如:LVPECL 訊號由於其具有快速上升和下降時間的原因一般都將如此),那麼加至時脈的 AM 雜訊被轉換為 PM 雜訊的機會就非常少,甚至完全沒有機會。

另外,大多數新式 ADC 要求以差動方式驅動時脈輸入,以實現最佳性能。時脈訊號佈線在PCB 上常常經過相當長的距離,因為訊號的源和目的地相互之間透常不是靠得很近。與單端時脈訊號傳送相比,以差動形式傳送時脈訊號可使訊號不受耦合影響,而且能全面提升設計的可靠性。

圖 1 所示 LO 訊號一般由鎖相迴路 (PLL) 系統產生。PLL 需要一個基準時脈,以將 LO 鎖定在該時脈上。傳統上,10MHz 是常見的基準頻率。不過,頻率高得多的基準時脈如今變得越來越普遍了。事實上,100MHz 以及更高的頻率在新式 RF 設計中並非不常見。

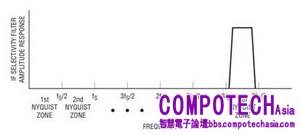

基準時脈透常由 OCXO 或 TCXO 元件產生,這種時脈的抖動 (或相位雜訊) 一般非常小。如果 PLL 基準時脈的頻率合理選擇為高於 RF 接收透道頻寬 (或在兩個或更多相鄰透道同時數位化的接收器中,為多個透道的頻寬) 的兩倍,那麼同樣的基準訊號還可用作 IF 取樣 ADC 的時脈,以符合某些適合的頻率規劃。理想情況下,IF 選擇濾波器的透帶及其過渡區域的大部分都應該在 ADC 的單一奈奎斯特 (Nyquist) 區域內,以避免頻率折疊。用圖 3 所示的 IF 濾波器幅度回應,可以說明這一點。在圖 3 中,所選 IF 與 ADC 的 7 階奈奎斯特區域相匹配。在該圖中,fS代表 ADC 的取樣速率。在這種情況下,會選擇圖 1 中的 LO,這樣,混頻器的下變頻訊號輸出就會以 IF 選擇濾波器的中間點為中心,如圖 3 所示。

圖 3:IF 濾波器幅度回應 (對於一種可避免頻率折折疊的ADC 取樣速率) 實例

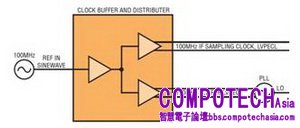

圖 4 總結了上述時脈分配方案,圖中假定基準頻率為 100MHz。圖 4 中的時脈緩衝器和分配器在這個系統中有很重要的作用,因為它接收來自 OCXO 或 TCXO 元件的單端正弦波,並提供兩個差動 LVPECL 訊號,這兩個訊號適合發送到 ADC 和 PLL。為了使在所分配的時脈上附加的抖動最小。LTC6957-1 是一款附加抖動很小的雙 LVPECL 輸出時脈緩衝器,適用於要求附加抖動較小的應用,並滿足上述討論中提出的所有要求。運用不同版本的 LTC6957,還可以實現其他輸出格式。LTC6957-2 提供 LVDS 輸出,LTC6957-3 和 LTC6957-4 提供 CMOS 輸出。

圖 4:基準時脈分配方案

電路實現

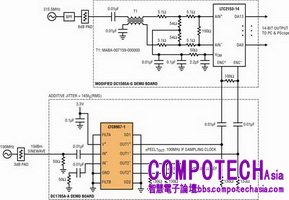

正如之前所討論的,抖動是提高 IF 的主要限制因素之一。用常見 ADC 和 LTC6957-1 構成時脈分配器時,能實現什麼樣的性能? 為了確定這一點,我們修改了兩款凌力爾特展示電路板,,並將兩塊展示電路板連接起來,如圖 5 所示。

圖 5:IF 取樣系統原理圖,該系統採用兩塊凌力爾特展示電路板以及 315.5MHz 輸入測試頻率和 100MHz 基準時脈

LTC2153-14 是一款 310Msps、14 位 ADC,該 ADC 為高的類比輸入頻率工作而進行了全面規定,使其適合在這應用中作為 IF 取樣 ADC 使用。其演示電路板 DC1565A-G修改後如圖 5 所示。

展示電路 DC1765A-A 採用了 LTC6957-1,用來緩衝 100MHz OCXO 的正弦波輸出。DC1765A-A 的兩對差動 LVPECL 輸出之一連接至 DC1565A-G 的差動編碼時脈輸入。第二對差動訊號可以用作圖 1 中 LO產生 PLL 訊號的基準輸入。

考慮到該 ADC 的時脈頻率為 100MHz,所以在避免混疊的同時,理論上能實現的最大頻寬為 50MHz。如圖 3 所示,選定了 7 階奈奎斯特區域,這意味著,該 50MHz 理想頻寬涵蓋了 300MHz 至 350MHz 頻率範圍。這就需要理想的磚牆式帶通濾波器,且濾波器的中心頻率為 325MHz,通帶為 50MHz,以允許僅300MHz 至 350MHz 範圍內的 IF 訊號通過,同時抑制其他所有在想要的頻帶中可能引起混疊和干擾的訊號。

在一個實際濾波器中,除了中心頻率容限,由於濾波器通帶和阻帶區域之間的過渡區域並非無限小,所以在這種情況下,更合理的 IF 頻寬選擇也許是例如頻寬高達 30MHz、中心頻率為 325MHz 的表面聲波 (SAW) 濾波器。目前此頻率範圍的 SAW 濾波器已越來越容易取得了。

性能總結

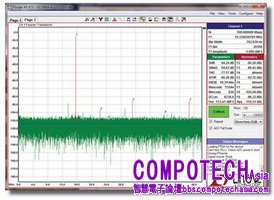

透過一個類似於 IF 選擇性濾波器的 BPF 和一個衰減器 (其用於把 ADC 所承受的幅度調整至-1dBFS) 可將一個 315.5MHz 測試音調連接至改良型 DC1565A-G 的類比輸入。DC1565A-G 透過 USB 連接至一台 PC,在此,PScope1資料獲取控制軟體用於監視兩個影響接收器品質的關鍵性參數:SNR 和 SFDR。圖 6 顯示運行中的PScopeTM,其提供當採用 315.5MHz、-1dBFS 音調作為 ADC 的類比輸入,並利用作為 ADC 編碼時脈的 LTC6957-1 對 100MHz LVPECL 訊號進行緩衝時的 131072 點 FFT 以及一些相關的分析。由圖 6 可見,實現的 SNR 高於 64dB,而 SFDR 則超過了 80dB。對於 325MHz IF 取樣器而言,這些指標參數是極其優異的。

圖 6:PScope的螢幕顯示圖說明 FFT 和所測得、圖 5 所示系統的訊號完整性參數

由於 LTC6957-1 的輸入是一個100MHz 正弦波 (為 50Ω 負載輸送 +10dBm 功率),因此按照 LTC6957 產品手冊所提出的建議,應把有助於在輸入為低幅度和/或低頻率時減小附加抖動量的內部頻寬限制濾波器 (FILTA 和 FILTB) 均關斷。

結論

我們在此設計並評估一個作為 RF 接收器一部分的325MHz IF 取樣系統。在此採用低抖動時脈緩衝器和分配器 LTC6857-1 以 LVPECL 格式來分配將被用作 ADC 取樣時脈和 PLL 基準的 100MHz 系統基準時脈。該 IF 取樣系統的性能是透過觀察 SNR 和 SFDR 數值來測量,透過該系統可獲得卓越的 64dB SNR 和傑出的 80dB SFDR,而實現了有助放寬 RF 鏡頻抑制濾波器要求的較高 IF 取樣。

注:

1PScope收集和分析來自 ADC 的時間域及頻率域的資料,並顯示相關參數 (可從www.linear.com下載)。