達到最高的Σ-Δ ADC驅動器的性能 (Part 1)

前言:

放大器級的設計由兩個彼此相關的不同級組成,因此問題變得難以在數學上建模,特別是因為有非線性因素與這兩級相關。第一步是選擇用來緩衝感測器輸出並驅動ADC輸入的放大器。第二步是設計一個低通濾波器以降低輸入頻寬,從而最大限度地減少帶外雜訊。

簡介

您有沒有檢查過網路上有多少筆關於“ADC緩衝器設計”的內容?答案是超過400萬筆,在如此多的參考文獻中,很難找到我們所需要的內容。對於大多數類比和混合訊號資料擷取系統設計工程師而言,這可能不是很意外,因為設計無緩衝類比數位轉換器(ADC)的外部前端需要具備耐心和大量建議。它常常被視為一種藝術形式,是經過多年摸索方能掌握其竅門的。對於不具經驗的人來說,這是一個令人沮喪的反覆嘗試過程。大多數時候,由於相互關聯的規格要求很多,迫使設計人員不得不進行很多權衡(和評估)才能達到最佳效果。

您有沒有檢查過網路上有多少筆關於“ADC緩衝器設計”的內容?答案是超過400萬筆,在如此多的參考文獻中,很難找到我們所需要的內容。對於大多數類比和混合訊號資料擷取系統設計工程師而言,這可能不是很意外,因為設計無緩衝類比數位轉換器(ADC)的外部前端需要具備耐心和大量建議。它常常被視為一種藝術形式,是經過多年摸索方能掌握其竅門的。對於不具經驗的人來說,這是一個令人沮喪的反覆嘗試過程。大多數時候,由於相互關聯的規格要求很多,迫使設計人員不得不進行很多權衡(和評估)才能達到最佳效果。

挑戰

放大器級的設計由兩個彼此相關的不同級組成,因此問題變得難以在數學上建模,特別是因為有非線性因素與這兩級相關。第一步是選擇用來緩衝感測器輸出並驅動ADC輸入的放大器。第二步是設計一個低通濾波器以降低輸入頻寬,從而最大限度地減少帶外雜訊。

放大器級的設計由兩個彼此相關的不同級組成,因此問題變得難以在數學上建模,特別是因為有非線性因素與這兩級相關。第一步是選擇用來緩衝感測器輸出並驅動ADC輸入的放大器。第二步是設計一個低通濾波器以降低輸入頻寬,從而最大限度地減少帶外雜訊。

理想的放大器是提供剛剛好的頻寬以正確緩衝感測器或變送器產生的訊號,而不會增加額外雜訊,並且功耗為零,但實際放大器與此相距甚遠。在大多數情況下,放大器規格將決定整體系統性能,尤其是在雜訊、失真和功耗方面。為了更進一步釐清此問題,第一步是瞭解離散時間ADC的工作原理。

離散時間ADC獲得連續時間類比訊號的樣本,然後將其轉換為數位碼。當訊號被採樣時,根據類比轉換器的類型,同一固有問題有兩種不同的情況。

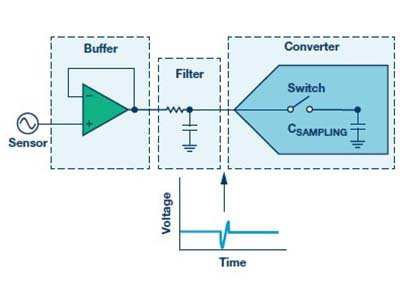

SAR ADC整合一個採樣保持器,其基本上由一個切換開關和一個電容組成,作用是保持類比訊號直到轉換完成,如圖1所示。

圖1:採樣保持電路圖

離散時間Σ-Δ ADC或過採樣轉換器實現了類似的輸入級,即具有一定內部電容的輸入切換開關。Σ-Δ ADC的採樣機制略有不同,但採樣輸入架構類似,使用切換開關和電容來保持類比輸入訊號的副本。

在這兩種情況下,切換開關都是用CMOS製程實現,閉合時電阻為非零值,通常為幾歐姆。此串聯電阻與採樣電容(pF級)的組合,意味著ADC輸入頻寬常常非常大,在許多情況下要遠大於ADC採樣頻率。

頻寬問題

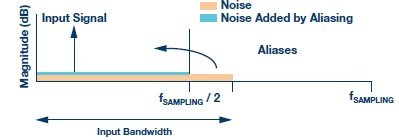

對轉換器來說,輸入訊號頻寬是一個問題。在採樣理論中,我們知道高於奈奎斯特頻率(ADC採樣頻率的一半)的頻率訊號應被移除,否則這些頻率訊號將在目標頻帶中產生鏡像或混疊。通常,雜訊頻譜中有相當一部分功率存在於ADC奈奎斯特頻率以上的頻帶中。如果不處理這種雜訊,它將混疊到奈奎斯特頻率以下,增加本底雜訊(如圖2所示),使系統的動態範圍明顯降低。

對轉換器來說,輸入訊號頻寬是一個問題。在採樣理論中,我們知道高於奈奎斯特頻率(ADC採樣頻率的一半)的頻率訊號應被移除,否則這些頻率訊號將在目標頻帶中產生鏡像或混疊。通常,雜訊頻譜中有相當一部分功率存在於ADC奈奎斯特頻率以上的頻帶中。如果不處理這種雜訊,它將混疊到奈奎斯特頻率以下,增加本底雜訊(如圖2所示),使系統的動態範圍明顯降低。

圖2:奈奎斯特折疊鏡像

ADC輸入訊號頻寬,以及緩衝器輸出頻寬,是第一個要解決的問題。為確保雜訊不會向下混疊,必須限制ADC輸入訊號的頻寬。這不是一個小問題。

通常,放大器的選擇是基於大訊號頻寬(即壓擺率)和增益頻寬積的規格,以便應對輸入訊號的極端情況,這決定了ADC可以追蹤的最快變化的訊號。

然而,放大器的有效雜訊頻寬等於小訊號頻寬(通常針對小於10 mV p-p的訊號而考慮),這常常比大訊號頻寬高出至少四到五倍。

換句話說,如果大訊號規格是針對500 kHz而選擇,那麼小訊號頻寬很容易就能達到2 MHz或3 MHz,這可能會導致ADC採集到大量雜訊。因此,在將類比訊號輸入ADC之前,應在外部限制小訊號頻寬,否則測得的雜訊將是ADC產品手冊規格的三到四倍。

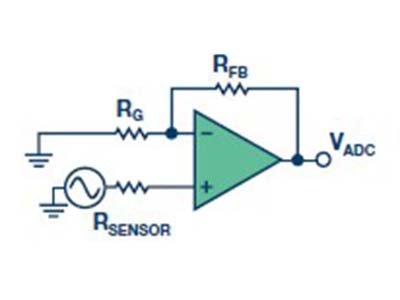

圖3:同相放大器配置

圖3:同相放大器配置

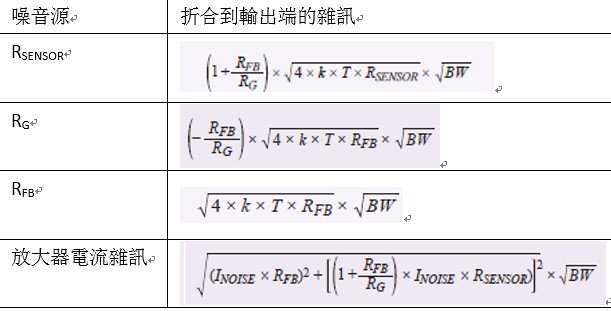

表1:放大器折合到輸出端的雜訊,RTO

記住,放大器產生的熱雜訊取決於放大器增益和總系統頻寬。電路示例如圖3所示,雜訊音源總結在表1中,其中:

T為溫度(單位為K),

k為玻爾茲曼常數(1.38 × 10−23 J/K),

電阻值單位為Ω,

BW指小訊號頻寬。

T為溫度(單位為K),

k為玻爾茲曼常數(1.38 × 10−23 J/K),

電阻值單位為Ω,

BW指小訊號頻寬。

以上公式表明,在ADC輸入針腳之前增加一個具有足夠衰減性能的低通濾波器以使採樣雜訊最小是很重要的,因為雜訊與頻寬的平方根成比例。通常,採用分立電阻和電容實現截止頻率足夠低的一階低通濾波器可消除大部分寬頻雜訊。一階低通濾波器還有一個額外的好處,即降低目標頻帶之外的任何其他較大訊號的幅度,防止其被ADC採樣而可能產生混疊。

但是,這還沒結束。ADC內部切換開關電阻和電容定義了類比輸入頻寬,但由於輸入訊號的變化,會產生時域充放電迴圈。每次切換開關(連接到採樣ADC電容的外部電路)閉合時,內部電容電壓可能與先前儲存在採樣電容上的電壓不同。

何為反沖(Kickback)問題?

下面是一個經典的類比問題:“若有兩個並聯電容連接到一個切換開關,開關斷開時,一個電容儲存了一些能量,那麼當切換開關閉合時,兩個電容會發生什麼?”

下面是一個經典的類比問題:“若有兩個並聯電容連接到一個切換開關,開關斷開時,一個電容儲存了一些能量,那麼當切換開關閉合時,兩個電容會發生什麼?”

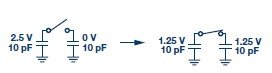

答案取決於充電電容儲存的能量和電容之間的比率。例如,如果兩個電容具有相同的值,則能量將在它們之間均分,電容端子間測得的電壓將減半,如圖4所示。

圖4:充電(左)和未充電(右)的電容

這就是反沖問題。

一些ADC會執行內部校準以補償內部誤差,這稱為自穩零校準。這些程式會使採樣電容電壓接近供電軌或另一電壓,例如基準電壓的一半。

這意味著放大器緩衝的外部訊號和採樣電容(其必須保存類比值以便擷取新樣本)常常不是處於相同的電位(電壓)。因此,採樣電容必須充電或放電,以使其與緩衝器輸出具有相同的電位。此過程所需的能量將來自外部電容(低通RC濾波器中的電容)和外部緩衝器。這種電荷再分配和電壓的建立將需要一定的時間,在此期間電路中各點處的電壓將受到干擾,如圖1所示。再分配的電荷量可能很大,相當於電流流入或流出放大器並流入電容。

結果是放大器應當能夠在非常有限的時間內對低通濾波器的外部電容和ADC的採樣電容進行充電/放電,低通濾波電阻則會用作限流器。

更具體地說,放大器應當能夠在給定誤差範圍內從採樣電容和外部源對電容充電/放電。外部低通濾波器的截止頻率應該比目標頻段略高一點,由濾波器的時間常數、ADC的位元數以及樣本之間的最差情況轉換(即我們應當能夠準確測量的最差輸入階躍)來定義。

如何解決反沖問題?

解決該問題的較簡單方法,是選擇具有足夠壓擺率、頻寬增益積、開環增益和CMRR的放大器,並將您在市場上能夠找到的最大電容放在輸出端,而電阻足夠小,以滿足低通濾波器頻寬要求。

解決該問題的較簡單方法,是選擇具有足夠壓擺率、頻寬增益積、開環增益和CMRR的放大器,並將您在市場上能夠找到的最大電容放在輸出端,而電阻足夠小,以滿足低通濾波器頻寬要求。

由於電容非常大,反沖問題將可以忽略不計,頻寬受低通濾波器限制,所以問題得以解決,對嗎?

很遺憾,上面的解決方案不會奏效,但如果您很好奇,想嘗試上述解決方案,那麼您會發現兩點:電容將像煉乳容器那麼大,放大器不喜歡輸出端有虛部阻抗。

放大器的性能取決於放大器看到的虛部阻抗。在這種情況下,低通濾波器的缺點是THD和建立時間性能降低。建立時間的增加將導致放大器無法對電容充電,使得ADC採樣的電壓不是正確的最終電壓。這將加劇ADC輸出的非線性。

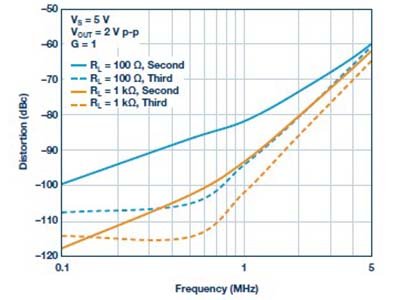

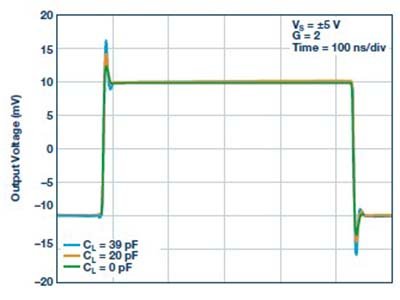

為了更好地闡述上面的觀點,圖5顯示了放大器驅動不同阻性負載的性能差異。圖6顯示了容性負載引起的小訊號過沖,這會影響建立時間和線性度。

圖5:AD4896-2 THD性能與負載的關係

圖6:ADA4896-2的小訊號傳輸回應與負載的關係

為了最大限度地解決這個問題,放大器輸出應通過低通濾波器的串聯電阻與外部電容隔離。

電阻應足夠大,以保證緩衝器不會看到虛部阻抗,但又足夠小,以滿足所需的輸入系統頻寬,並使緩衝器流出的電流在電阻上引起的IR壓降最小(放大器可能無法足夠快地使這種電壓降穩定下來)。

同時,電阻應支援外部電容減小到足夠小的值,以最小化反沖而不影響建立時間。

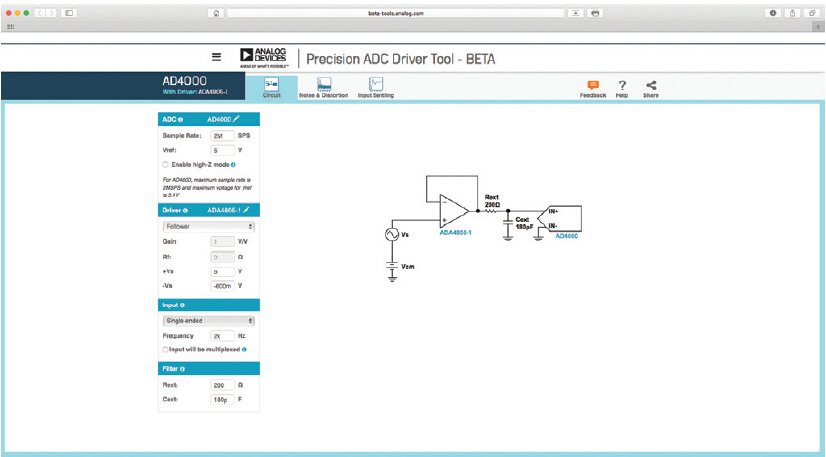

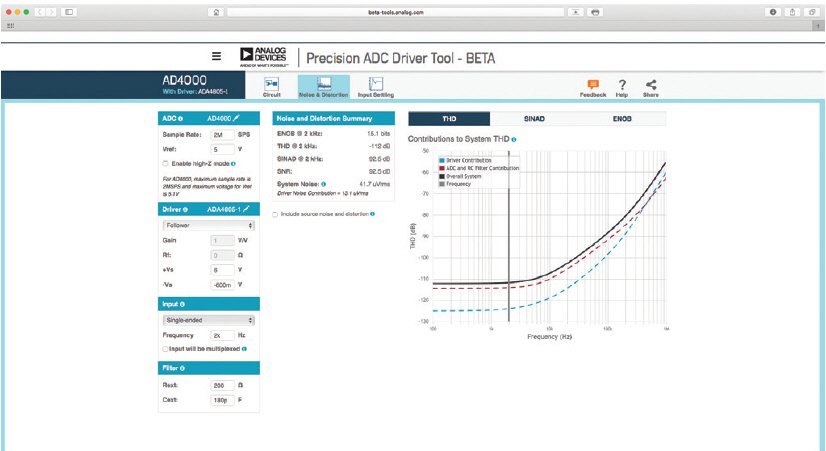

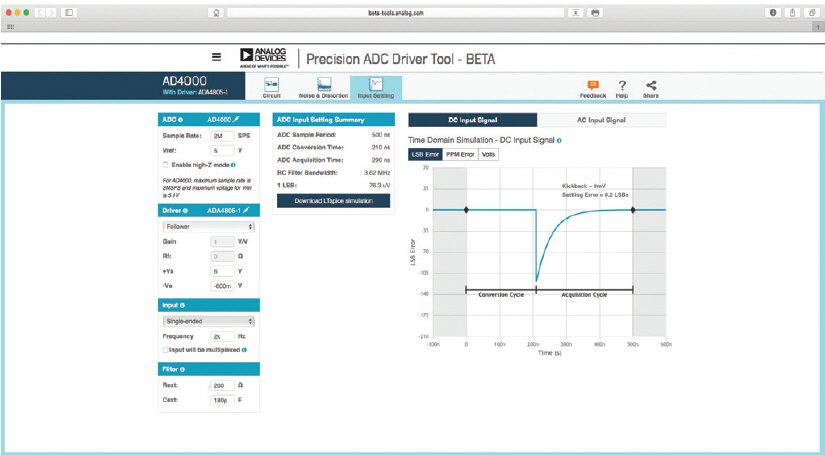

幸運的是,有一些工具可以讓我們預測ADC、放大器和濾波器的組合性能,比如說精密ADC驅動器工具。

此工具可以對反沖、雜訊和失真性能進行模擬,如圖7所示。

圖7:精密ADC驅動器工具的各種模擬

(本文作作者:ADI產品應用工程師Stuart Servis 及 線性與精密技術部的應用工程師Miguel Usach Merino)