在今年稍早我所發表一篇名為”The ABCs of Interleaved ADC交錯式ADC(類比數位轉換器)的原理(About),效益(Benefit)與挑戰(Challenge)”的文章當中,我探討了交錯式技術的基礎。交錯式技術多項優勢展現在許多的市場領域中,從通訊到量測設備一直到軍事/航太等領域都有。每個領域都有應用可以因為交錯式ADC的優點而獲益。在通訊基礎架構當中,追求更高取樣速率的動機在於實現多重波段、多重載波的無線電。除此之外,更高的取樣速率也會為能夠使用於線性化技術像是DPD(數位預失真)等的更大頻寬鋪路。在軍事以及航太市場當中,更高取樣速率的ADC能夠實現通訊、電子監控、與雷達等方面的多用途系統。在工業儀器當中,更高取樣速率的ADC讓供應商可以設計出能夠精確量測更高速信號的設備。就像一般的情況一樣,我們可以看到天底下沒有白吃的午餐。交錯式ADC也有它自己要面臨的一套挑戰。當會造成突波的交錯式ADC處於fS/2 與 fS/2 ± fin的ADC輸出頻譜當中時,我們就會觀察到各種的不匹配。這些不匹配是因為兩組交錯式轉換器之間的偏移、增益以及時序的差異所造成的。在本文中我們將會更加深入其特性、優點以及挑戰當中,而且還不僅只是這些。我們將會檢驗因為不同的不匹配量所造成的突波強度。

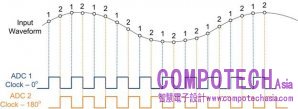

首先回想一下將兩組ADC交錯時,取樣速率會以2的係數而增加。這也將會以2的係數而延伸個別的耐奎斯特區域,將現有的運作頻寬加倍。注意到在圖1當中,180o的時脈相位關係以及取樣是如何交錯的。輸入波形會由兩組ADC交替取樣。在此情況下,交錯的執行是利用以時脈輸入除以2的係數,以及被路由至每個ADC時脈的所需相位。增加的作業頻寬可以為許多市場區塊的應用裝置帶來許多的好處。無線電系統可以增加支援波段的數量;雷達系統可以改善空間解析度,而量測設備可以實現更大的類比輸入頻寬。

圖1:兩種交錯式ADC – 時脈以及取樣

就像以往從交錯式技術的原理、效益與挑戰開始一樣,我們將會從更深入檢視偏移不匹配的突波開始。你應該會記得,兩組ADC之間的偏移不匹配會產生在fS/2的突波。因此我們要如何才能知道這個突波有多強以及其未來會如何呢?我們來看看下列的公式1a,其中的OffsetMismatch是以編碼數量而給定。

公式1a:

現在假設我們有一個雙通道交錯式元件(在此範例中為AD 9286)當中兩組8位元ADC之間的典型偏移不匹配。此大約為額定值滿量程的0.4%。此所代表的編碼數量應該是28的0.4%,亦即1.024。將此代入公式1b之後,我們獲得如下:

公式1b:

此將獲得一個很有趣的結果。滿量程的0.4%偏移不匹配似乎沒有太大的誤差,但是它會造成一個相當大的、具有– 41.94 dBFS強度的偏移突波。目前大部分使用於高速ADC的應用裝置都無法容忍此類型的突波。此將會主宰交錯式ADC的無雜散動態範圍(SFDR)。大部分的應用裝置需要至少70 dBc的SFDR,而針對多重載波GSM(MC-GSM)應用盡可能要達到85 dBc。這是為何AD 9286具有偏移調整功能的數個原因之一,此可以讓使用者精細微調每個ADC的偏移,藉以將偏移不匹配最小化。此外,由於突波的位置是在fS/2,因此它可能會被任何使用於ADC類比輸入上的抗鋸齒濾波器(AAF)過濾掉。為了要對偏移突波獲得一些額外的深入瞭解,下方的圖2當中顯示了fS/2突波與ADC之間偏移不匹配量的關聯性圖表。

圖2:偏移突波 vs. 偏移不匹配(交錯式8位元ADC)

此提供我們一個很有趣的畫面。為了要符合典型的70 dBc(- 71 dBFS)雜散需求,因此對於8位元轉換器的偏移不匹配必須要低於滿量程的0.025%。這很難在圖表當中辨識出來,但是為了要符合MC-GSM的典型規格,因此偏移不匹配必須低於0.0025%。這會讓我們思考偏移需要匹配到多接近才足夠。偏移必須要非常的匹配才行。下一步是來看看增益偏移的數學。這將會讓我們看到有多少的增益不匹配轉換成處於fS/2 ± fin的交錯突波。

為了要藉由增益不匹配計算在fS/2 ± fin下突波的強度,我們必須使用下列的公式2a。在這個公式當中,VFS1 與 VFS2都是兩組已經成為交錯式ADC的滿量程峰值對峰值電壓。

公式2a:

現在假設我們有一個雙通道交錯式元件(例如AD 9286)當中兩組8位元ADC之間的典型增益不匹配。通常此大約是額定值滿量程的0.05%。這代表的是ADC1具有2 VP-P的滿量程電壓,而ADC2則具有1.999 VP-P的滿量程電壓。將這些數字代入公式2a之後,可以得到如下的公式2b:

公式 2b:  = 72.04 dBc

= 72.04 dBc

現在這個結果似乎好多了。這個不匹配造成了處於fS/2 ± fin的72 dBc突波。此符合我們先前曾經討論過的70 dBc或是更好的位準。這仍然可能會主宰交錯式ADC的無雜散動態範圍(SFDR)規格。大部分的應用裝置需要至少70 dBc的SFDR,但許多應用裝置則需要更好的SFDR。舉例來說,就像我們先前所討論過的偏移不匹配,在MC-GSM中,85dBc或是更好的SFDR需求往往是必要的。讓我們來看看我們必須要到達何處才能符合或是超越85 dBc位準。在下方的圖3當中顯示的是增益不匹配突波的強度相對於以滿量程百分比表示之增益不匹配的關係。

圖3:增益突波 vs. 增益不匹配(交錯式8位元ADC)

此圖表給了我們一些很好的資訊以及對於我們所能容許增益不匹配位準的更深入洞察。為了要符合典型的70 dBc雜散需求,當我們在此處檢查時,增益不匹配必須要低於8位元轉換器滿量程的0.05%。在像是AD 9286這樣的元件當中,大約滿量程的0.05%典型增益不匹配就可以讓我們達成所期望的70 dBc規格。這會讓我們思考兩組ADC之間的增益需要匹配到多接近才足夠。假如我們可以透過另一個0.025%來減少不匹配,那麼我們就能夠將增益不匹配突波降低至78 dBc。假如我們可以更加的深入並且將不匹配降低至0.005%,那麼我們就可以使突波下降到92 dBc。為了要使突波強度降低至85 dBc,增益不匹配不能多於滿量程的0.01%。這告訴了我們所要面對的是什麼,因此我們知道能夠在容許多少不匹配的情況下,依然可以符合典型的系統需求。

現在我們已經檢視過來自於偏移與增益不匹配的突波強度,接著我們要來將因為時序不匹配所造成的突波位準加以量化。就在增益突波以fS/2 ± fin出現時,因為時序不匹配所產生的突波也會以fS/2 ± fin出現。這個討論的結果將會提供我們判定處於fS/2 ± fin的突波有多少是因為增益不匹配而造成,有多少則是由於時序不匹配所導致的資訊。這點相當重要,因為在交錯式ADC能夠分辨出導致突波振幅主要出自於哪一種不匹配時,它會相當的有幫助。瞭解這點可以讓設計者將焦點放在對於fS/2 ± fin下之交錯式突波貢獻最多的不匹配上。我們所希望的是不要落到一個兩種不匹配都很明顯的位置上,而且會造成大量不希望出現處於fS/2 ± fin的交錯式突波。最佳的作法就是在設計過程的一開始就將增益以及時序不匹配最小化。

檢視下列公式3a當中的計算,並且檢查因為時序不匹配所導致的突波計算。我們會看到突波位準是操作頻率(ωA)以及時序不匹配(ΔτE)的乘積。

公式3a:

現在,讓我們假設我們有一個在雙通道元件中介於兩組ADC之間的典型時序不匹配。其典型值應該大約是500 fs。將此代入公式3a當中,我們會獲得如公式3b的下列結果:

公式3b: =  76 dBc

76 dBc

這個結果相較於先前的增益不匹配範例多了一些激勵。500 fs的時序不匹配會造成在fS/2 ± fin下的76 dBc交錯式突波。比起大部分應用裝置所能夠容忍的最大突波位準(70 dBc)還低了數個dB。這仍然會輕易的主宰交錯式ADC的無雜散動態範圍(SFDR)規格。第二與第三諧波以及其它的雜散應該最有可能低於70 dBc。我們希望讓它更降低一些,因為會有一些我們已經使用過的應用 (像是MC-GSM範例)會需要85 dBc或是更好的無雜散動態範圍。在下方的圖4當中展示了時序不匹配突波的強度相對於以皮秒(picosecond)計算之時序不匹配的關係。

圖4:時序突波 vs. 時序不匹配(交錯式14位元ADC)

此圖表為我們說明了幾件事情。類似於增益不匹配圖表,突波強度大致會呈現指數衰減,而一旦不匹配接近到10 ps時,突波強度的圖形會變成幾近平坦的狀態。同時,它也告訴我們必須要讓時序不匹配非常的小(毫微微秒(femtosecond)範圍),藉以使突波強度落入90 dBc的範圍內。為了要符合MC-GSM應用裝置的85 dBc規格,低於200 fs的時序不匹配是有其必要的。這會讓我們思考兩組ADC之間的時序必須要匹配到多接近才足夠。當我們說毫微微秒時,那真的是非常短的時間!然而,由於製程技術的縮短以及匹配技術的改善,要將交錯式ADC之間時序的不匹配最小化已經變得比較容易了。然而,佈局與電路設計只是謎題的一部分而已。在高速ADC正在推向達到千兆取樣範圍運作的今天,設置某些類型的校正,藉以降低交錯式ADC之間的增益、偏移、與時序不匹配是有其必要性的。那雖然已經有些超出了本文所討論的範圍,但仍然是必須要注意的重點。在某些情況下,對這些不匹配以數位方式補償而非在類比域進行可能會比較容易。

具有更廣大頻寬運作標準的最新通訊系統設計、具有更嚴格空間解析度需求的先進雷達技術、以及超高頻寬量測設備似乎不斷的在超越現有的ADC技術。這些需求推動著ADC的使用者與生產廠商去開發出能夠跟上這些需求腳步的方法。相較於典型ADC提高轉換速率的傳統路徑,交錯式ADC允許以更快的速度達成更大的頻寬。透過將兩組或是更多ADC結合與交錯在一起,現有的頻寬將獲得提昇,而系統設計需求也能夠以更快的速度達成。然而交錯式ADC不會憑空而來,而ADC之間的不匹配也無法予以忽略。在本文中所提出的公式有助於計算處於fS/2 與 fS/2 ± fin下之突波(因為偏移、增益、以及時序不匹配所造成)的預期位準。即使不匹配確實存在,瞭解它們並計算出它們位於何處以及其振幅,對於處理它們來說都是一個相當好的起點。擁有這些知識讓設計者可以適當的處理這些突波,並且更聰明的使用交錯式ADC,以便符合他們最新系統設計的需求。