簡介:寬帶隙技術之承諾

在當下功率電子應用中,需要降低整體解決方案尺寸的同時,提升能效和可靠度,該目標隨時隨地都存在。這些應用包括電動車牽引變頻器、數據中心轉換器和UPS、太陽能/風能採集以及數以億計的世界各地家庭和辦公室每天使用的為高科技裝置供電之小型轉換器。

寬帶隙(WBG)電源開關已經面市以應對這些挑戰。用WBG元件代替傳統的矽功率半導體可將典型DC / DC轉換器的效率從85%提升到近95%,或將典型DC / AC變頻器之效率從96%提升至99%。

在當下市場上的WBG元件中,氮化鎵(GaN)高電子遷移率電晶體(HEMT)相較現有基於矽的替代品(例如超級結電晶體)具有顯著優勢,具備高達約600V之額定電壓。其他優勢還包括WBG還具有顯著的低輸入和輸出電容(Ciss和Coss),從而可降低開關損耗。此外,GaN電晶體的米勒電容(Miller capacitance)遠低於具有同樣大小RDS(ON)的MOSFET。因此,GaN元件可以更快速地開啟和關斷,從而允許使用尺寸更小的變壓器和被動元件。此外,每個晶片面積的導通電阻更低,具有更低的傳導損耗,從而使設計人員能夠在能量損耗、元件尺寸以及熱管理(如散熱器)系統的成本和尺寸之間實現非常有利的平衡。

市場上的氮化鎵

直到最近,相較更加成熟的基於矽的替代品,氮化鎵技術一直是非常昂貴。超級結電晶體的發展,雖然進一步改善了矽片技術之品質因數,但卻一直是阻礙GaN元件廣泛採用的因素之一。然而,隨著GaN技術的進一步開發和規模經濟之作用,使GaN在經濟上更具有可行性,市場對於更進一步提升功率轉換的性能表現和效率依然具有迫切需求,GaN元件已經完全準備好以獲得越來越多的設計採用。

基本上,氮化鎵功率電晶體或者是耗盡型(depletion-mode)元件或是增強型元件(e-mode),耗盡型元件通常處於導通狀態,需要相對於汲極和源極負閘極電壓來關斷。這些元件通常是關斷狀態,並需要正閘極電壓來實現導通。

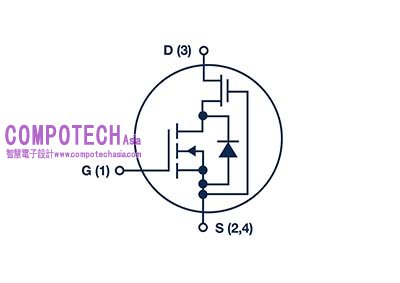

耗盡型元件可以提供更高的性能表現和牢固性,但需要認真管理系統啟動以避免潛在的危險短路。例如,在使用耗盡型GaN FET作為上下兩個開關的半橋拓撲架構中,必須首先啟動閘控制電路以提供負偏壓並保持電晶體關閉,以防止將DC排流線加電到短路。另一種方法是使用帶低壓矽MOSFET的疊接配置耗盡型GaN電晶體。如圖1所示,GaN電晶體源極連接到矽MOSFET汲極,而矽MOSFET源極連接到GaN電晶體閘極。在沒有偏壓被施加到矽MOSFET閘極時,其汲極 - 源極電壓(Vds)負偏置到GaN電晶體閘極,以保持元件關斷。安森美半導體NTP8G202NG等共同封裝的疊接GaN功率電晶體已經投放市場。

圖1:Cascode配置能夠提供通常關斷便利的GaN性能表現優勢。

增強型GaN HEMT通常關斷,消除了啟動時的短路問題。諸如650V GaN Systems GS66516B這樣的元件可僅以0-6V的低閘極電壓進行操作,閘極處容許的瞬態電壓高達-20至+10V,進一步簡化了設計。憑藉6個觸點和一個專為底側冷卻而設計的封裝,以及25mΩ的低導通電阻,它可以處理高達10A的漏源電流,而開關頻率可高達10MHz。

開關電路設計

像其他功率元件一樣,氮化鎵電晶體需要適當匹配和配置的閘極驅動器,以確保元件快速實現完全的開啟和關斷,而不會出現意外問題。為了達到這個目的,驅動器必須能夠快速為電晶體的閘極電容充電來導通元件,而不會引起振鈴或過衝。當關斷時,必須迅速放電閘極,還是不能有振鈴或過衝。一致的性能表現和正確的延遲時間(skew-time)控制是必不可少的,以避免橋接配置中的「直通(shoot-through)」短路。

驅動GaN元件時需要考慮三個關鍵因素,分別是最大允許閘極電壓、閘極閾值電壓和體二極管壓降。由於GS66516B等增強型GaN元件的閘極 - 源極電壓為6V或大約是MOSFET的一半,因此更容易產生所需的導通/關斷電壓和電流。閘極電壓也具有較低的負溫度係數,這簡化了驅動器補償。電晶體本身體二極管的正向電壓降比同類矽MOSFET高大約1V。

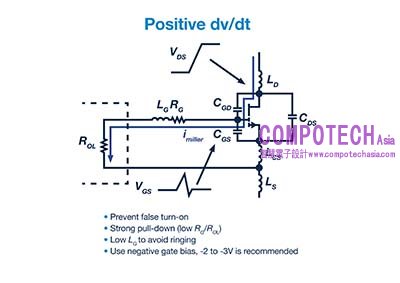

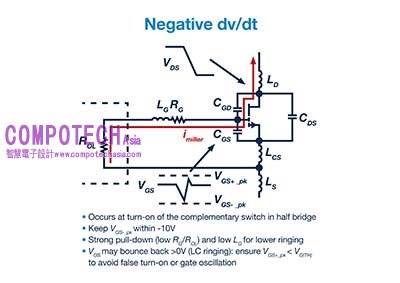

GaN的總體導通時間比具有相同RDS(ON)的MOSFET快四倍左右,而關斷時間約快兩倍。雖然這帶來了系統級的優勢,但在考慮驅動器和相關電路的動態問題時需要特別小心。 dV / dt轉換速率可能快於100 V / ns,這可能會在開關轉換期間在橋中的配對元件之間出現「直通」,從而對效率產生不利影響。

為了防止這種情形發生,可以調節閘極驅動上拉電阻,以達到最快的理想轉換時間,同時不至於引起其他不需要的之損耗。此外,這有助於避免過沖和振鈴,因此可以防止誤開啟/關斷毛刺,並最大限度地減少EMI之產生。在實際中,可能還需要添加與閘極串聯的鐵氧體磁珠以減少高頻LC振鈴和過衝,並可能在閘極-源極路徑上增加一個RC「緩衝器」。

圖2以繪圖的方式總結了GaN電晶體之導通情形,並突出了需要考慮的問題以確保可靠的操作。同樣,圖3顯示了關斷情形。

圖2:安排GaN電晶體導通時需要考慮之因素。 (來源:GaN Systems)。

圖3:GaN電晶體關斷情形(來源:GaN Systems )。

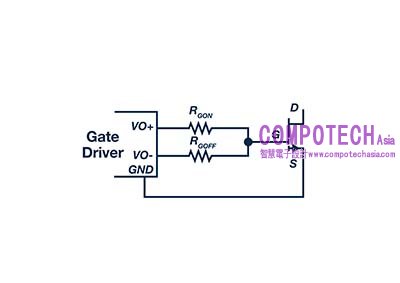

對於電壓閾值較低的GaN元件,僅透過分離驅動器中的閘極上拉和下拉連接,可以單獨地在導通和關斷條件下優化上拉電阻,並允許插入一個離散電阻(圖4) 。

圖4:獨立優化開啟和關斷電阻有助於減少不良影響(來源:GaN Systems)。

為了最大限度地提升驅動器之性能表現和穩定性,優化閘極導通/關斷電阻比是必要的。導通閘極電阻通常在10到20Ω之間,如果太大,導通dV / dt轉換速率會降低,因而導致開關速度變慢並增加損耗。反過來,如果轉換速率太低,米勒效應導通以及潛在的閘極諧振都可能引起開關損耗。如果導通閘極電阻為10-20Ω,則通常需要大約1-2Ω的關斷電阻,以便在阻抗最小的情形下進行快速、穩健之下拉。

閘極驅動器的選擇

TI LMG1205等閘極驅動器IC都是為應對許多驅動GaN電晶體的細微之處而設計,同時仍然允許用戶根據定制設計來選擇元件、開關速度和其他考量。 LMG1205針對增強型裝置進行了優化,可以在同步降壓、升壓或半橋配置中驅動高側(high-side)和低側(low-side)開關。高側和低側輸出之獨立輸入能夠為設計人員提供很大靈活性。該驅動器可以提供高達1.2A的電流,汲入最大5A的電流,以防止在過渡期間產生不必要之導通,並具有分離式閘極輸出,可以使每種情形下的電流可以得到獨立優化。

另外,為了在驅動高側和低側開關時確保高效率,並避免直通,LMG1205具有35ns(典型值)的低傳輸延遲,這可以實現通道之間在1.5ns內匹配。

與LMG1205一樣,Silicon Labs的Si827x系列、Analog Devices 的ADuM4223A / B系列以及Maxim的MAX5048C,都是專門設計用於驅動GaN元件,設計者可以使用現有的MOSFET驅動器,只要它具有合適的性能表現和特性,開關頻率也相對較低。

除了選擇最合適的驅動器和設計周邊電路外,設計人員還必須考慮所有常見問題,以確保功率半導體的正確開關。這些舉措包括優化電路佈局和走線以盡量減少雜訊電感,並將驅動器盡可能靠近電晶體閘極放置,以最大程度減少外部閘極至汲極之耦合。可能還需要開爾文源(Kelvin-source)連接來最小化共源電感,也可以考慮電隔離的電源軌。

結論

商用氮化鎵功率電晶體的擊穿電壓額定值高達600V,目前已上市,使電源設計人員能夠利用寬帶隙半導體相對於超級結電晶體等矽元件的性能表現優勢。為了充分利用新元件卓越的速度和特性,需要仔細設計導通/關斷電路,其中包括將高頻設計之原理應用於可靠開關和最佳能效設計。