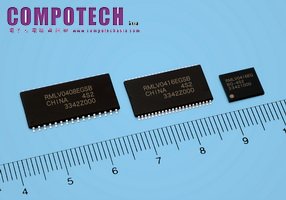

2013年10月8日--先進半導體解決方案之頂尖供應商瑞薩電子(TSE:6723)宣佈將推出12款RMLV0416E、RMLV0414E及RMLV0408E系列先進低功率SRAM (Advanced Lower-Power(LP) SRAM)新產品,為瑞薩的旗艦SRAM (靜態隨機存取記憶體)。新款記憶體裝置具有4 Mb密度,並採用電路線寬僅110 nm(奈米)的精密製程技術。

上述即將推出之SRAM為全新系列的先進低功率SRAM,並提供與瑞薩現有採用150 nm製程之SRAM產品相同的高可靠性,包括無軟體錯誤(註1)及無閂鎖(註2)。這些產品可在標準電流2 µA(微安培)、25°C下達到低功率運作,適合用於以電池備份之裝置中的資料儲存。

瑞薩的低功率SRAM已在多種領域獲得廣泛的採用,包括工業、辦公室、通訊、汽車及消費性產品,該公司此類產品在2012年並擁有全球第一的市佔率(註3)。近來由於製造商系統已達到更高的效能與更先進的功能,SRAM已成為提升整體系統可靠性的重要因素。特別是用於儲存重要資訊如系統程式與帳單資料的SRAM,必須提供高水準的可靠性,因此焦點也特別放在降低因α輻射與宇宙中子輻射造成之軟體錯誤的方法。

在瑞薩的先進低功率SRAM架構中,記憶體單元中的每個記憶體節點(註4)皆附加實體電容器(註5),因此對於軟體錯誤具有極高的耐受性。在發生軟體錯誤之後,一般的處理方法是在SRAM或製造商系統中納入內部錯誤修正碼(ECC)電路。但是此方法有其限制,在一些情況下,ECC的效能可能無法處理影響多個位元的錯誤。相較之下,先進低功率SRAM採用結構性方法以避免軟體本身發生錯誤。

從目前大量生產之150 nm先進LP SRAM的系統軟體錯誤評估結果而言,實際上這些產品稱得上是無軟體錯誤。

另外,SRAM單元負載電晶體(P通道)為多晶矽TFT (註6),且堆疊於矽基板上的N通道MOS電晶體頂端。因此,只有N通道電晶體會形成於矽基本之下。如此可確保記憶體區域中不會形成任何寄生閘流體,而且理論上將不可能產生閂鎖。

這些功能使先進低功率SRAM所達到的可靠性遠高於採用傳統記憶體單元結構的全CMOS類型(註7)產品。對於非常重視高水準可靠性的應用而言,例如工廠自動化設備、測量裝置、部署於智慧電網的設備以及運輸系統等,先進低功率SRAM將有助於進一步提高這類應用的效能與可靠性。

此外,先進低功率SRAM結合SRAM多晶矽TFT堆疊技術與堆疊式電容器技術以縮小單元尺寸。例如,110 nm先進低功率SRAM的單元大小相當於採用65 nm製程的全CMOS SRAM。

除上述產品外,瑞薩也將計劃加入8 Mb與64 Mb的110 nm產品以強化其110 nm SRAM產品陣容。

供貨時程

瑞薩電子新款SRAM將自2013年11月開始供應樣品,並預定自2013年12月開始量產。(供貨時程如有變更,將不另行通知。)

關於瑞薩電子

瑞薩電子株式會社(TSE:6723)為全球第一的微控制器供應商,同時也是SoC系統晶片與各式類比及電源裝置等先進半導體解決方案的領導品牌之一。經由NEC電子(TSE:6723)與瑞薩科技的業務整合,瑞薩電子自2010年4月1日起正式營運,業務範圍則涵蓋了各種應用裝置的研發、設計與生產。總部位於日本的瑞薩電子,子公司遍及全球20個國家,如欲了解更多資訊,請造訪www.tw.renesas.com。

(註1)軟體錯誤:

指一種現象,當外部α或中子輻射撞擊矽基板時會產生電荷,導致儲存於記憶體中的資料遺失。相對於可再現的硬體錯誤,例如半導體元件的硬體故障,軟體錯誤無法再現,而且只需由系統重新寫入資料即可修正錯誤。一般而言,軟體錯誤的發生率會隨著製程愈趨精密而提高。

(註2)閂鎖:

指一種現象,由CMOS電晶體的井區、矽基板、P型擴散層及N型擴散層形成的NPN或PNP結構(寄生雙極電晶體)因來自電源供應器或輸入腳位的過電壓而進入導通狀態,允許大電流流入電源供應器與接地之間。

(註 3) 資料來源:瑞薩電子。

(註4)記憶體節點:

各記憶體單元中將資訊位元儲存為「高」或「低」電位的正反器電路節點。

(註5)堆疊式電容器:

由多晶矽或金屬產生兩個電極的電容器。這些電容器產生於矽基板上的MOS電晶體上層,有效降低記憶體單元的表面積。

(註6)薄膜電晶體(TFT):

由薄膜多晶矽產生的電晶體。這些元件做為SRAM負載電晶體使用,產生於矽基板上的MOS電晶體最上層,有效降低記憶體單元的表面積。

(註7)全CMOS類型:

由產生於同一矽基板表面總計六個P通道MOS電晶體與N通道MOS電晶體所構成的SRAM記憶體單元結構,它具有較大的表面積,因此有發生閂鎖的風險。