賽靈思設計方法資深行銷總監Tom Feist表示:「我們為系統設計人員擴充抽象層的數量和種類,不僅協助目前的硬體客戶提升生產力,更讓系統和軟體工程師能直接運用All Programmable FPGA、SoC和3D IC進行編程。」

加速硬體設計

為加速在All Programmable元件中進行高度整合的複雜設計,賽靈思推出了Vivado® IP Integrator (IPI),可透過Vivado高階合成(Vivado HLS)技術加速整合客戶IP、Xilinx LogiCORE™和 SmartCORE™ IP、第三方IP、MathWorks採用賽靈思System Generator的Simulink設計與C/C++和System C合成IP。

Ganinspeed公司軟體和FPGA部門總監Ties Bos表示:「Vivado IPI和HLS的結合對Ganinspeed新一代有線架構產品的開發而言非常可貴,讓我們得以透過以軟體為主的完全IP架構加快全新服務的開發。這種結合各種編程抽象化的方法可讓我們利用C++開發各種演算法,快速整合最終的IP,而且比RTL設計流程節省15倍以上的開發成本。」

Vivado IPI採用ARM® AXI互聯技術和針對IP封裝的IP-XACT元數據等業界標準,可針對採用賽靈思All Programmable解決方案的設計與提供智慧型自動建構校正功能進行最佳化。當嵌入式設計團隊決定採用Zynq™-7000 All Programmable SoC進行設計後,能使用更快的方法來辨識、重用和整合鎖定雙核心ARM處理系統和高效能FPGA架構的軟硬體IP。

加速系統級設計

系統工程師偏愛用C/C++/SystemC、OpenCL、MathWorks MATLAB與 Simulink,以及NI LabVIEW™等編程語言的抽象化方法為現今更智慧型系統 (smarter system) 的軟硬體製作模型。賽靈思和其聯盟計畫成員協助設計團隊直接執行這些演算法,且不必對執行細節有所顧慮。

MathWorks已在其R2013b版本中針對Zynq-7000 All Programmable SoC元件發佈了全新設計流程指南,提供軟體開發人員和硬體設計工程師用MATLAB 和 Simulink的環境編寫他們的演算法和建立模型,也可分割設計中的軟體和硬體,在賽靈思的目標設計平台自動進行鎖定應用、整合、除錯和測試哪些模型。這項功能以MathWorks廣泛的特定應用工具套件函式庫和穩固的嵌入式軟硬體程式碼編程技術為基礎,協助使用者驗證並將系統效能最佳化,進而讓更多開發人員在設計中運用業界第一款All Programmable SoC,並充分發揮其優勢。

嵌入式系統設計人員使用LabVIEW 和 NI® 的可重配置 I/O (RIO) 硬體將傳統的RTL設計的複雜度進行高層次的抽象化,免除了因部署目標應用建置作業系統、驅動程式和中介軟體等曠日廢時的作業。國家儀器為嵌入式設計建置了一個平台式的方案,其中包括了現成、可重新配置的硬體和直覺式的圖形程式介面;只要點擊一下,NI LabVIEW 2013開發環境即可在NI的目標應用上進行編譯、除錯和部署各種為處理器或可編程邏輯編寫的應用程式,且支援多款賽靈思All Programmable元件。NI為其超過60個可部置目標應用的平台選用賽靈思All Programmable SoCs 和 FPGA做為RIO運算核心。

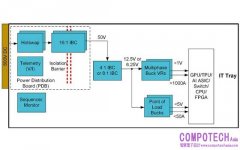

賽靈思與多家早期採用的客戶合作開發一個全新的系統級異質平行編程環境,可支援軟體的編程、系統驗證、除錯和自動執行C/C++ 和 OpenCL程式語言。全新且完善的Eclipse™環境將提供適用於特定市場的函式庫,可大幅提升設計生產力。此設計流程專為系統設計師、軟體應用程式開發人員和需要平行運算架構的嵌入式設計人員量身打造,讓他們透過簡易的方法即可提升系統效能、降低系統物料清單(BOM)成本、減少整體功耗,並可追趕上ASSP、DSP和GPU的開發時間。

加速軟體設計

賽靈思All Programmable Abstractions也可加快Zynq-7000 All Programmable SoC 和 MicroBlaze™處理器的軟體開發。賽靈思已開發了一個名為Quick Emulator (QEMU)的開放原始碼虛擬機器,可模擬系統的各種軟硬體介面,能提早在系統開發前期即能完成軟體開發,可帶來更高的生產力和持續不斷的軟硬整合驗證。

此外,賽靈思也與Cadence公司合作,鎖定賽靈思的Zynq-7000 All Programmable SoC提供虛擬化系統平台,可同時進行軟硬體開發,大幅節省開發成本和縮短產品上市時程。設計團隊一起運用這些虛擬化環境和賽靈思開發套件(SDK),可將系統開發時程提前數月。

欲進一步瞭解賽靈思如何透過All Programmable Abstractions領先一個世代的相關資訊,請瀏覽www.xilinx.com/apa網站。

關於賽靈思

賽靈思公司(Xilinx, Inc.;NASDAQ:XLNX)是全球All Programmable FPGA、SoC與3D ICs的領導廠商。這些業界領先的元件與其新一代設計環境和IP相結合,將能滿足客戶對於可編程邏輯系統整合的多元需求。欲瞭解更多賽靈思公司資訊,請瀏覽www.xilinx.com網站。

- SailPoint 升級 AI 平台,以適應性身分

- Palo Alto Networks 發表業界最安全、專

- 意法半導體與 Leopard Imaging 推出支援

- Rohde & Schwarz 實現新一代 Wi‑Fi

- Universal Robots 和 Scale AI 聯合推出模

- 工研院2026 VLSI TSA國際研討會4月

- 華為雲尚海峰:出海迎來三大新趨

- 願景到落地:NEC台灣與Avaloq攜手舉

- SailPoint 與 AWS 簽署策略合作協議 透

- Palo Alto Networks 推出新世代信任安全

- Supermicro 推出全新 Gold Series 企業伺

- AI代理人時代來臨 企業架構準備好