全球電子設計創新領導廠商益華電腦 (Cadence Design Systems, Inc.),今日推出AWR 設計環境® V16版本 (簡稱AWR V16),具備突破性的跨平台互用性,整合Cadence® Virtuoso® 設計平台以及Allegro® PCB與IC封裝設計平台,支持高頻射頻(RF)到毫米波 (mm Wave) IP異質技術開發。V16版本亦導入與Clarity™ 3D求解器和Celsius™ 熱求解器的無縫整合,為大規模複雜RF系統的電熱性能分析,提供不受拘束的處理量。最新AWR設計環境,包含AWR Microwave Office® 電路設計軟體,讓客戶得以高效地為汽車、雷達系統和半導體技術設計5G無線與連接系統,且更快上市。與其他工作流程相比,V16版中平台和求解器整合所減少的周轉時間 (TAT) 高達50%。

Cadence研發副總裁Vinod Kariat表示:「為了在競爭激烈的5G/無線市場獲勝,客戶需要能實現完整且全面RF工作流程的解決方案,這些工作流程不僅只在晶片上展開和停止,而是延伸至整個系統。AWR V16版本所實現的RF工作流程創新,始於現今共享且跨產品間無縫轉移設計資料與軟體IP造就出的基礎優勢。在Cadence旗下,V16版本導入RF整合程度將大幅提升工程團隊的生產力」。

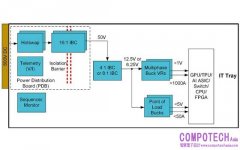

平台互用性是推動RF整合與提升工程生產力的重要關鍵。在AWR設計環境、Virtuoso和Allegro平台間無縫共享設計資料,消弭RF設計與製造佈局團隊之間的任何脫節、節省寶貴工程資源且正向影響開發時程。隨著V16版本導入深度電磁 (EM) 與內建熱分析,客戶可以減少了3倍的周轉時間。

V16版本關鍵功能包括:

整合Allegro:確保和PCB及IC封裝設計流程的製造相容性與RF整合

整合Virtuoso:利用AWR Microwave Office進行RF前端設計IP,並結合Virtuoso 佈局套裝(Layout Suite),進行IC和模組的整合。

整合Clarity:實現針對大型RF結構設計驗證的電磁分析,例如模組封裝和相位陣列饋入網路 (phased-array feed networks)

整合Celsius :為MMIC 和PCB高功耗RF應用提供熱分析

增強AWR功能:利用設計自動化與FEA求解器效能增強,加速高頻射頻(RF) IP建立。

HRL實驗室先進封裝解決方案事業群主管Florian Herrault說道:「具備整合EM求解器技術的AWR設計環境、Allegro PCB/SiP以及Virtuoso RF等Cadence 平台,對我們高頻射頻 (RF) /毫米波(mmWave) MMIC、RFIC和多晶片2.5/3D封裝技術的開發至關重要。我們設計團隊因Cadence RF解決方案所獲得的效能和生產力增益而興奮不已。在AWR Microwave Office裡能與我們的IC、封裝與電路板團隊共享所建立的RF IP,大幅減少整體設計時間,更快速地將最高品質產品推向市場」。

AWR設計環境V16版本支持Cadence 智慧系統設計策略,加速實現系統單晶片 (SoC) 設計與系統創新。V16平台現已釋出且現可供下載。如欲了解更多詳細資訊,請造訪網址: www.cadence.com/go/AWRV16 。

關於Cadence

Cadence在運算軟體領域擁有超過30年的經驗,已為當今電子設計的領導者。公司以智慧系統設計 (Intelligent System Design) 為核心策略,提供軟體、硬體及半導體IP,協助電子設計從概念走向應用實現。Cadence服務全球客戶,從晶片、印刷電路板至整體系統打造尖端與創新的電子產品,以應用於行動、消費性電子、超大型運算、5G通訊、汽車、航太、工業及健康醫療等當今最活躍的市場。Cadence 已連續七年榮獲財星雜誌(FORTUNE)評列「百大最佳職場」之肯定。詳細Cadence 資訊,請見 cadence.com .

本月熱點 HOME

- SailPoint 升級 AI 平台,以適應性身分

- Palo Alto Networks 發表業界最安全、專

- 意法半導體與 Leopard Imaging 推出支援

- Rohde & Schwarz 實現新一代 Wi‑Fi

- Universal Robots 和 Scale AI 聯合推出模

- 工研院2026 VLSI TSA國際研討會4月

- 華為雲尚海峰:出海迎來三大新趨

- 願景到落地:NEC台灣與Avaloq攜手舉

- SailPoint 與 AWS 簽署策略合作協議 透

- Palo Alto Networks 推出新世代信任安全

- Supermicro 推出全新 Gold Series 企業伺

- AI代理人時代來臨 企業架構準備好