對於數位波束成形相位陣列而言,要生成LO,通常會考慮的實現方法是向分佈於天線陣列中的一系列鎖相迴路分配常用基準頻率。對於這些分散式鎖相迴路,目前文獻中還沒有充分記錄用於評估組合相位雜訊性能的方法。在分散式系統中,共同噪音源是相關的,而分散式噪音源如果不相關,在RF 訊號組合時就會降低。對於系統中的大部分元件,這都可以非常

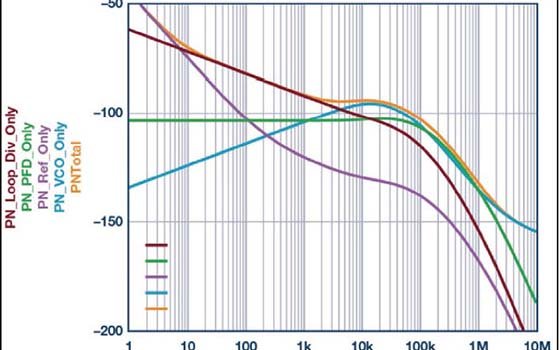

直覺地加以評估。對於鎖相迴路,迴路中的每個元件都有與之相關聯的雜訊傳遞函數,它們的貢獻是控制迴路以及任何頻率轉換的函數。這會在嘗試評估組合相位雜訊輸出時增加複雜性。

直覺地加以評估。對於鎖相迴路,迴路中的每個元件都有與之相關聯的雜訊傳遞函數,它們的貢獻是控制迴路以及任何頻率轉換的函數。這會在嘗試評估組合相位雜訊輸出時增加複雜性。

本文基於已知的鎖相迴路建模方法,以及對相關和不相關貢獻因素的評估,提出了跟蹤不同頻率偏移下的分散式PLL 貢獻的方法。

圖:典型的鎖相迴路相位雜訊分析,顯示所有元件的雜訊貢獻。總雜訊是所有貢獻因素的總和。