隨著 AI 運算需求的指數型成長,運算、記憶體、電源管理及互連架構對效能與能源效率的要求日益提升,強化資料中心內的光學互連與光纖數量也將不斷增加,為協助超大規模運算業者突破這些限制,意法半導體導入矽光子與次世代 BiCMOS 技術,宣布推出新一代專屬技術,強化資料中心與 AI 叢集的光學互連效能,提供 800Gb/s 及 1.6Tb/s 光學模組,並計畫於 2025 年下半年量產。

意法半導體的射頻與光通訊事業部總經理Vincent Fraisse提及意法半導體的雲端光學互連技術願景,是建立在三大核心基礎之上。第一,邊緣 AI(Edge AI)。預期在未來五年內,邊緣 AI 的運算效能將提升100 倍。

第二,資安(Security)。必須保護日益增加的裝置數量,以防範不斷提升的網路攻擊威脅。

第三,雲端 AI(Cloud AI)。不僅負責處理與雲端之間的數據傳輸,也能補足邊緣運算,形成邊緣到雲端的運算整合架構。意法半導體認為,AI 基礎架構正邁入全新的發展時代,未來所有伺服器元件都將透過光學連結或互連技術相互整合。

雲端運算中心基本上由四大核心關鍵元素構成:運算、記憶體、電源與互連。

意法半導體憑藉技術領先優勢,致力於解決現今資料中心在高效能與能源效率的挑戰,透過現有與新一代技術,專注於這四大核心中的兩個關鍵領域:第一,電源供應(Power Supply)。第二,互連技術(Interconnect)。

AI 的快速發展推動資料中心對更高效能、更大頻寬的需求,但更重要的是,提升能源使用效率。全球超大規模運算業者(Hyperscaler)面臨的挑戰,在於如何最佳化每單位運算的功耗,以及每位元傳輸的功耗。

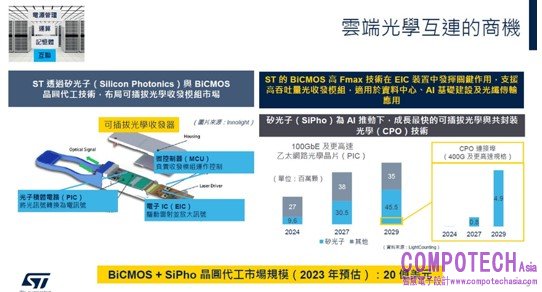

雲端光學互連的商機

Vincent Fraisse表示,AI 的快速發展推動資料中心對更高效能、更大頻寬的需求,但更重要的是,提升能源使用效率。全球超大規模運算業者(Hyperscaler)面臨的挑戰,在於如何最佳化每單位運算的功耗,以及每位元傳輸的功耗。意法半導體擁有最佳的 BiCMOS 技術,可用於打造 EIC 元件,其關鍵技術指標(KPI)專為這類應用量身設計。但更重要的是,我們認為大多數收發模組正逐步將 PIC 遷移至矽光子技術(SiPho),無論是可插拔光學模組或共封裝光學模組(CPO),SiPho 都將成為未來的發展趨勢。

矽光子技術在未來十年內將維持雙位數成長,主要受 AI 叢集需求推動。

這項成長將來自資料中心連接埠數量的增加,以及這些連接埠所需的高速運作能力。目前的傳輸速度為 800Gbps,而未來將提升至 3.2Tbps。這將帶動未來十年的網路發展,預期BiCMOS 與矽光子晶圓代工市場在 2030 年將達 20 億美元。

可插拔收發模組帶來的優勢

與現有的 EML 和 VCSEL 技術相比,未來需考量的一個重要因素是,矽光子技術能為可插拔收發模組帶來的優勢。矽光子技術提供更卓越的效能,支援更長的傳輸距離。當這些因素與市場對更高傳輸量的需求發展結合時,可以預見矽光子在未來幾年將成為收發模組市場的主要技術,甚至可能擴展至 CPO(共封裝光學)短距離銅線連接的應用領域。

矽光子技術的另一個優勢是,其效能提升可以轉換為功耗優勢,搭配更線性的 EIC 和 BiCMOS 技術,可透過移除 DSP 來降低系統功耗。這項技術已應用於特定類型的收發模組,稱為 LPO/LRO,即線性可插拔光學模組(Linear Pluggable Optic)或線性接收光學模組(Linear Receiver Optic)。透過提供更穩定、更線性且損耗更低的訊號,可以省略 DSP 的連接階段,進一步降低功耗。此外,矽光子技術憑藉更優異的效能,使 LPO 和 LRO 可支援更長的傳輸距離。

全新的矽光子技術平台——PIC 100

意法半導體早在十年前便是矽光子技術的先驅,但當時市場尚未成熟,因此決定延後技術商轉。如今市場需求已經成熟,因此決定推出全新技術 PIC 100,並認為,這是目前唯一可支援每通道最高 200Gb 傳輸速率的純矽 12 吋技術。

PIC100 將受惠於位於法國克羅爾(Crolles)的 12 吋晶圓廠,並採用先進微影技術,其良率可達數位 CMOS 製程的水準。

PIC100 將為市場帶來矽光子技術的完整優勢,包括精巧的設計、更遠的傳輸距離,以及目前業界尚未達到的純矽整合技術效能。

此外,透過創新的材料堆疊技術,PIC100 使光纖可直接連接至光子 IC 的邊緣,而非傳統的垂直耦合方式,有效降低系統損耗,這也是所有光學傳輸開發者面臨的持續挑戰。

PIC 100 將於2025 年下半年進入量產階段。

意法半導體已與 AWS 簽署合作協議,AWS 深度參與了 PIC 100 的開發,並計畫在技術進入量產階段後,將其部署於基礎建設中。

此外,意法半導體也正與全球領先的光學解決方案供應商合作,這些市場領導者專注於可插拔光學收發模組,並計畫在其下一代 1.6T 收發模組中採用 PIC 100,應用於DCI(資料中心互連)與 AI 叢集。

晶片對晶片GPU 互連

Vincent Fraisse表示,轉向矽光子技術已是不可逆的趨勢,而全球最大的超大規模運算業者也認同這一點。然而,還有另一個市場正在興起,而矽光子技術將成為主要標準,這就是晶片對晶片(Chip-2-Chip)GPU 互連。

為了因應連接密度持續提升的需求並降低功耗,業界正逐步將機架後端的銅線連接替換為光學連接,並將其高度整合,使其符合 GPU 的物理尺寸要求。這正是部分業界人士所稱的CPO(共封裝光學)或光學 I/O(Optical IO),其概念是光纖將直接連接至 GPU。這類 光學 I/O 需要高密度調變器以維持精巧設計,客製化 EIC 解決方案來提升效能並適應不同應用需求,以及矽穿孔(TSV)來降低損耗,並透過3D 組裝提升密度。

意法半導體將透過 PIC100 設計平台,提供完整的技術工具組,協助 Optical IO 的開發與應用。

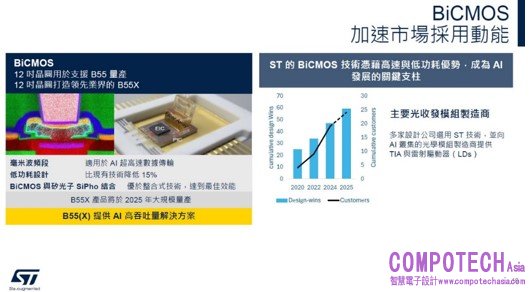

次世代BiCMOS 技術

意法半導體擁有最優秀的 BiCMOS 技術,可用於打造 EIC 元件。在線性度與雜訊表現,這些因素對於提升傳輸效能並降低每位元傳輸功耗至關重要,而 BiCMOS 技術展現了明顯的優勢。

意法半導體在這個市場擁有超過 10 年的豐富經驗,並持續向客戶提供 BiCMOS 技術。日前意法半導體將推出 BiCMOS 技術家族中的全新成員——B55 系列,其中最先進的技術版本為 B55X。

憑藉市面上最佳的最大震盪頻率(Fmax)、最高轉換頻率(FT)以及更低的雜訊表現,B55X 是單通道 200G 及下一代 400G 技術的理想選擇。其優異的線性度特性,特別適用於 LPO(線性可插拔光學模組),這類光學收發模組以低功耗、低成本為核心設計目標。

值得注意的是,LPO 採用無 DSP 設計,相較於傳統 DSP 架構方案,能大幅降低功耗並減少延遲,在系統層級對於超大規模運算業者而言具有顯著優勢。目前,設計導入正在加速推進,截至目前為止,已有約 20 家大型客戶正在採用 BiCMOS 技術設計 EIC。

除了純矽技術之外,意法半導體作為獨立的垂直整合製造商(IDM),能夠提供獨特的價值主張,涵蓋整個供應鏈的完整服務。意法半導體的矽光子技術與 BiCMOS 技術結合,構成業界獨有的 12 吋矽技術平台,專為光學市場服務。這兩項技術皆在位於法國克羅爾(Crolles)的 12 吋晶圓廠生產,確保穩定供應。

AI 正在改變市場發展 ST提供最佳解方

此外,意法半導體還提供晶片設計、組裝等服務,並特別針對電光測試(Electro-Optical Testing)提供完整解決方案,這對於希望將矽光子技術推向與 CMOS 相同服務水準的客戶而言,將極具價值。

AI 正在改變市場發展,帶動更高傳輸速度、更大頻寬,以及更高能源效率的技術需求。日前,意法半導體正式發表兩項關鍵技術矽光子技術 PIC100 及BiCMOS 技術,以回應這項趨勢。