JESD204B是最近批准的JEDEC標準,用於轉換器與數位處理器元件之間的串列資料介面。它是第三代標準,解決了先前版本的一些缺陷。該介面的優勢包括:資料介面路由所需電路板空間更少、設定與維持所需的時序要求更低,以及轉換器和邏輯元件的封裝更小。市場上已有多家供應商的新型類比/數位轉換器採用了此介面,例如ADI公司的AD9250。

與現有介面格式和協定相比,JESD204B更複雜、更微妙,但仍須克服一些困難才能實現其優勢。像任何其他標準一樣,要使該介面比單倍數據速率或雙倍數據速率CMOS/LVDS等常用介面更受歡迎,它必須能無縫地工作。雖然JESD204B標準是由JEDEC制定,但某些特定資訊仍需要闡明,或者可能分散於多種參考文獻。另外,如果有一個簡明的指南能概要說明該標準、工作原理以及如何排除故障,無疑對使用者將極為有幫助。

本文將闡述JESD204B標準之ADC與FPGA的介面,以及該如何判斷其是否正常工作,還有更重要的是,如何在發現問題時排除故障。本文討論的故障排除技術可以採用常用的測試與量測設備,包括示波器和邏輯分析儀,以及Xilinx ChipScope或Altera SignalTap等軟體工具。同時也將說明介面信號的傳輸,以便能利用一種或多種方法實現信號傳輸的視覺化。

JESD204B概述

JESD204B標準提供一種將一個或多個資料轉換器與數位訊號處理元件介面的方法(通常是ADC或DAC與FPGA介面),相比於典型的並列資料傳輸,這是一種更高速度的串列介面。該介面速度高達12.5 Gbps/通道,使用框架串列資料連結及嵌入式時脈和對齊字元。它減少了元件之間的軌跡(trace)數量,降低了軌跡匹配(trace-matching)要求,並消除了設定與維持時序的限制問題,從而簡化了高速轉換器資料介面的施行。由於訊號的連結(Link)需要在資料傳輸之前建立,因此存在了新的挑戰,必須採用新的技術來確定介面是否正常工作,以及在介面故障時該怎麼處置。

首先扼要說明該標準的工作原理。JESD204B通過三個階段來建立同步連結:代碼組同步(CGS:Code Group Synchronization)、初始通道同步(ILAS:Initial Lane Synchronization)和資料傳輸階段(Data Transmission Phase)。連結時需要以下信號:共用參考時脈(元件時脈),至少一個差分CML物理資料電氣連接(differential CML physical data electrical connection)(即所謂Lane,通道),以及至少一個其他同步信號(SYNC~和可能的參考同步訊號SYSREF)。使用哪些信號取決於Subclass(次層級):

Subclass 0 uses Device Clock, Lanes and SYNC~;

Subclass 1 uses Device Clock, Lanes, SYNC~ and SYSREF;

Subclass 2 uses Device Clock, Lanes and SYNC~.

Subclass 0在許多情況下足以滿足需求,因而是本文的重點。Subclass 1和Subclass 2提供了建立決定性延遲的方法,這在需要同步多個元件或需要系統同步或固定延遲的應用中非常重要,例如一個系統的某個事件需要已知的取樣緣(sampling-edge),或者某個事件必須在特定時間長度內回應輸入信號。

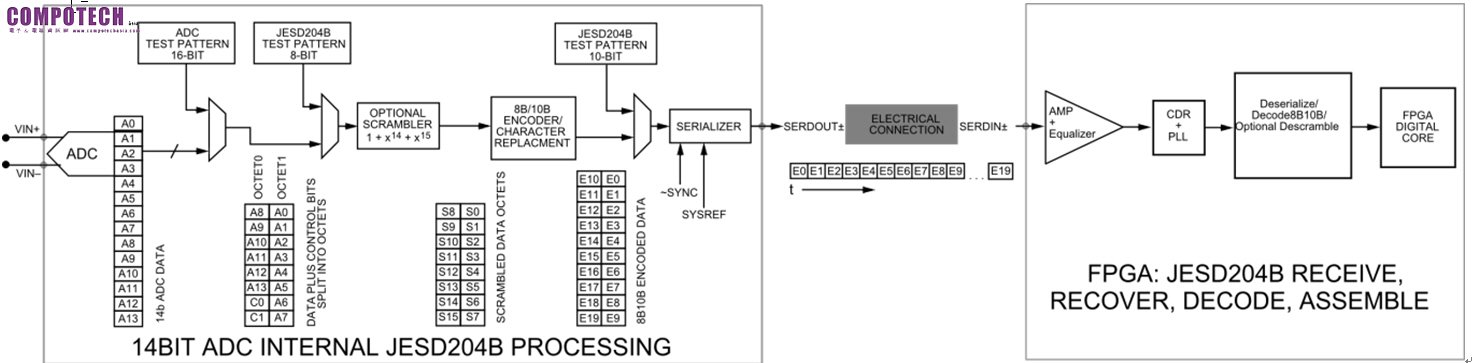

圖1顯示了從Tx元件(ADC)到Rx元件(FPGA)的簡化JESD204B連結,資料從一個ADC經由一個通道傳輸。

雖然JESD204B規範有許多變數,但某些變數對於連結的建立特別重要。這些關鍵變數如下所示(注:這些值通常表示為「X-1」):

- M : Number of converters轉換器數

- L : Number of Physical Lanes物理通道數

- F: Number of Octets per Frame, also每個框架的8位字數,以及

- K : Number of frames per Multiframe每個多重框架的框架數

- N &N’ : Converter Resolution and Number of bits used per sample (multiple of 4), respectively. N’ value is N value plus control and dummy bits. 分別表示轉換器解析度和每個樣本使用的位元數(4的倍數),N’的值等於N值加上控制和偽資料位元數。

Subclass 0:同步步驟

如上所述,許多應用可以採用相對簡單的Subclass 0工作模式,這也是建立和驗證連結的最簡單模式。Subclass 0通過三個階段來建立和監控同步:CGS階段、ILAS階段和資料階段。各階段相關的圖表以不同格式顯示資料,可以在示波器、邏輯分析儀或FPGA虛擬I/O分析儀(如Xilinx ChipScope或Altera SignalTap)上觀察到這些資料。

代碼組同步(CGS)階段

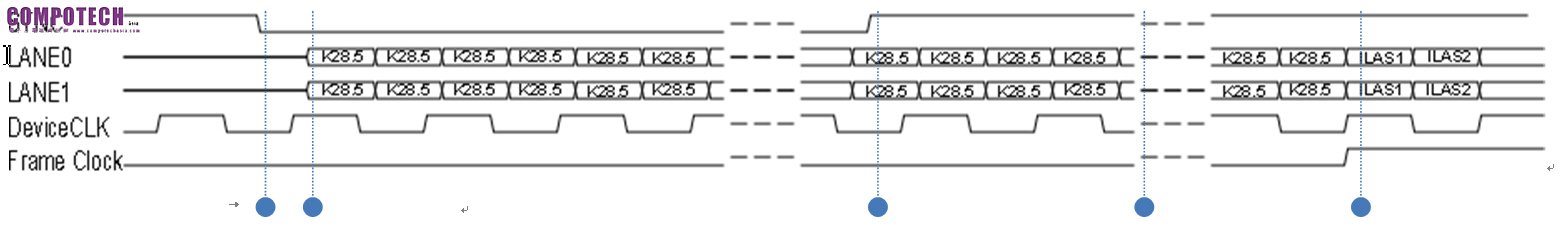

可以在連結上觀察到的CGS階段最重要部分如圖2所示,圖中五個特別標示的點說明如下。

圖2:JESD204B Subclass 0連結信號在CGS階段的邏輯輸出(假設有兩個通道,一個元件含兩個ADC)

1. RX將SYNC~接腳驅動至低電位,發出一個同步請求。

2. TX從下一個符號(symbol)開始,發送未擾碼(unscrambled)的/K28.5/符號(每個符號10位元)。

3. 當RX接收到至少四個無錯誤的連續/K28.5/符號時,RX同步,然後將SYNC~接腳驅動至高電位。

4. RX必須接收到至少四個無錯誤8B/10B字元,否則同步將失敗,連結留在CGS階段。

5. CGS階段結束,ILAS階段開始。

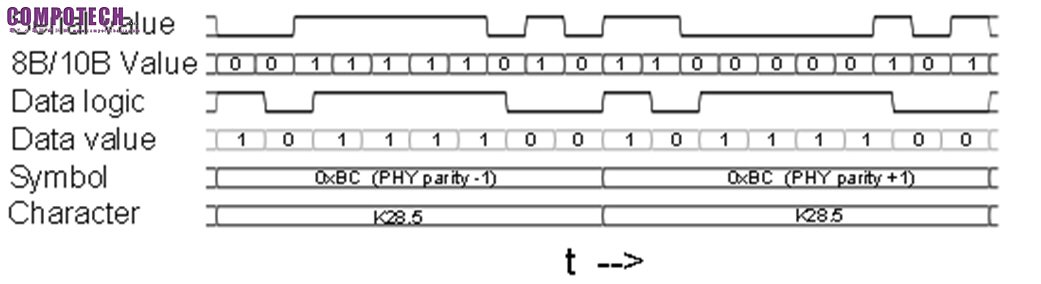

/K28.5/字元在JESD204B標準中也稱為/K/,如圖3所示。標準要求運行偏差(disparity)為中性。利用8B10B編碼,可以實現平均而言包含等量1和0的平衡序列。每個8B10B字元可能具有正(1較多)或負(0較多)偏差,當前字元的奇偶性由先前發送的字元的當前和決定,這通常是通過交替發送正奇偶性字與負奇偶性字來完成。圖中顯示了K28.5符號的兩種極性。

圖3:K28.5字元的邏輯輸出以及它如何通過JESD204B Tx信號路徑傳播

|

Serial Value |

串列值 |

|

8B/10B Value |

8B/10B值 |

|

Data logic |

資料邏輯 |

|

Data value |

數據值 |

|

Symbol |

符號 |

|

Character |

字元 |

請注意以下幾個重點:

l 「串列值」表示通過通道傳輸的10位元的邏輯電位,可透過測量物理介面的示波器看到。

l 「8B/10B值」表示通過通道傳輸的邏輯值(10位元),可透過測量物理介面的邏輯分析儀看到。

l 「資料值」和「資料邏輯」表示8B10B編碼前JESD204B Tx模組內符號的邏輯電位,可透過Xilinx ChipScope或Altera SignalTap等FPGA邏輯分析工具看到。

l 「符號」表示要發送的字元的十六進位值,請註明PHY層的奇偶性。

l 「字元」表示JEDEC規範中所指的JESD204B字元。

ILAS階段

ILAS階段有四個多重框架,允許RX對齊來自所有連結的通道,以及驗證連結參數。為了調和不同長度的軌跡以及接收器導致的字元偏斜,通道必須對齊。四個多重框架緊緊相連。無論啟用擾碼(scrambling)連結參數與否,ILAS始終是無擾碼傳輸。

完成SYNC~的去置位(de-asserted)後(變為高電位),便進入ILAS階段。發送模組內部跟蹤到(ADC內部)一個完整多重框架(multiframe)後,便開始發送四個多重框架。在所需的字元中插入偽取樣(dummy samples),以便傳送完整的多重框架,如圖4所示。四個多重框架包括:

l 多重框架1:以/R/字元[K28.0]開始,以/A/字元[K28.3]結束。

l 多重框架2:以/R/字元開始,後接/Q/ [K28.4]字元,然後是14個配置8位元字的連結配置參數(見表1),最後以/A/字元結束。

l 多重框架3:與多重框架1相同。

l 多重框架4:與多重框架1相同。

框架長度可以利用JESD204B參數計算:(M/L) × F × (1/取樣速率)

- 含義:(ADC數/通道數)*(8位字數/框架) × (1/取樣速率);

- 舉例:兩個ADC、兩個通道、每框架兩個8位元字(Octets),取樣速率為250 MSPS,則框架長度為8 ns。

o (2/2)×(2)×(1/250 MHz)= 8 ns

多重框架長度可以利用JESD204B參數計算:(M/L) × F × K (1/取樣速率)

- 含義:(ADC數/通道數)×(8位字數/框架)×(框架數/多重框架) × (1/取樣速率)

- 舉例:兩個ADC,取樣速率為250 MSPS,兩個通道,每框架兩個8位字,每個多重框架含三十二框架,則多重框架長度為:

o (2/2)×(2)×(32)×(1/250 MHz)= 256 ns

圖4:JESD204B Subclass 0連結信號在ILAS階段的邏輯輸出

表1:ILAS多重框架2的CONFIG表(14個JESD204B配置參數8位元字)

|

Octet# |

Bit7 (MSB) |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

BIT 1 |

BIT 0 (LSB) |

|

8位字數 |

位7 (MSB) |

位6 |

位5 |

位4 |

位3 |

位2 |

位1 |

位0 (LSB) |

|

0 |

DID[7:0] |

|||||||

|

1 |

ADJCNT[3:0] |

BID[3:0] |

||||||

|

2 |

|

ADJDIR |

PHADJ |

LID[4:0] |

||||

|

3 |

SCR |

|

|

L[4:0] |

||||

|

4 |

F[7:0] |

|||||||

|

5 |

|

|

|

K[4:0] |

||||

|

6 |

M[7:0] |

|||||||

|

7 |

CS[1:0] |

|

N[4:0] |

|||||

|

8 |

SUBCLASS[2:0] |

N’[4:0] |

||||||

|

9 |

JESDV[2:0] |

S[4:0] |

||||||

|

10 |

HD |

|

|

CF[4:0] |

||||

|

11 |

RESERVED #1 |

|||||||

|

12 |

RESERVED #2 |

|||||||

|

13 |

FCHK[7:0] |

|||||||

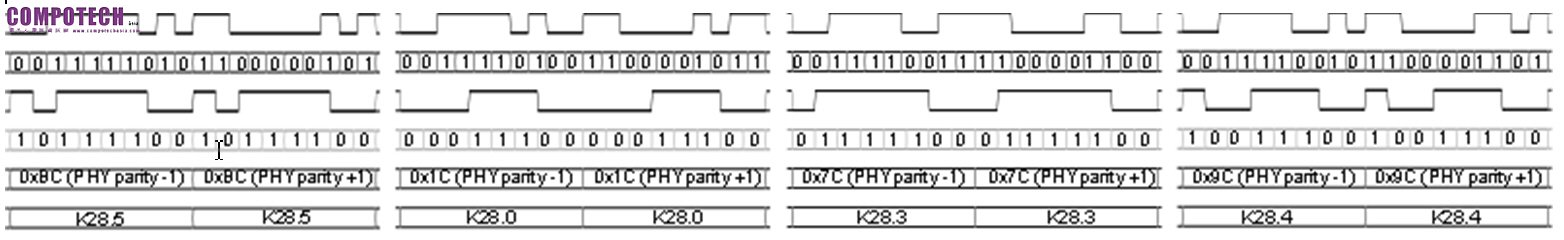

圖5:K字元[K28.5]、R字元[K28.0]、A字元[K28.3]和Q字元[K28.4]

|

a./K/ Character |

a. /K/字元 |

|

b./R/ Character |

b. /R/字元 |

|

c./A/ Character |

c. /A/字元 |

|

d./Q/ Character |

d. /Q/字元 |

資料階段(啟動字元替換)

在資料傳輸階段,通過控制字元監控框架對齊。在框架的結尾處執行字元替換。在資料階段,資料或框架對齊不會造成額外消耗。字元替換允許在框架邊界處發送對齊字元,唯一條件是當前框架的最後一個字元可以替換為上一框架的最後一個字元。這有利於(偶爾)確認自ILAS序列後,對齊不會改變。

出現下列情況時,會對發送器執行字元替換:

- 若關閉了擾碼,並且框架或多重框架的最後一個8位字等於上一框架的8位字。

- 若啟動了擾碼,並且多重框架的最後一個8位字等於0x7C,或框架的最後一個8位字等於0xFC。

發送器和接收器各自維護一個多重框架計數器(LMFC),它持續計數到(F*K)-1,然後繞回到0重新開始計數(忽略內部字元寬度)。向所有發送器和接收器發送一個公共(來源)SYSREF,這些元件利用SYSREF重置其LMFC,這樣所有LMFC應互相同步(在一個時脈週期內)。

釋放SYNC(所有元件都會看到)後,發送器在下一次(TX) LMFC繞回0時開始ILAS。如果F*K設置適當,大於(發送器編碼時間)+(線路傳播時間)+(接收器解碼時間),則接收資料將在下一個LMFC之前從接收器的SERDES傳播出去。接收器將把資料送入FIFO,然後在下一個(RX) LMFC邊界開始輸出資料。發送器SERDES輸入與接收器FIFO輸出之間的已知關係稱為「決定性延遲」(Deterministic Latency)。

**注意:‘204的資料階段具有零延遲,即資料階段一旦開始,則不存在對齊字元。字元替換允許在框架邊界處發送對齊字元,唯一條件是當前框架的最後一個字元可以替換為上一框架的最後一個字元。這有利於(間或)確認自ILAS序列後,對齊不會改變

哪些方面會出錯?

JESD204B可以說是一個複雜的介面標準,操作上有許多微妙之處。要找出不能正常工作的原因,需要對可能的情形有充分的瞭解:

陷入CGS模式:如果SYNC保持邏輯低電位,或者脈衝高電位持續時間少於四個多重框架:

1.檢查電路板,拔掉電源:

a. SYSREF和SYNC~信號應直流耦合。

b. 在電路板沒有通電的情況下,檢查從SYNC~源(通常來自FPGA或DAC)到SYNC~輸入(通常是ADC或FPGA)的電路板SYNC~連接是否良好且具有低阻抗。

c. 確認下箝位(pull down)或上箝位電阻沒有影響信號傳輸,例如:值太小或短路就會導致無法正確驅動。

d. 確認JESD204B連結的差動對軌跡(包括電纜,如果有使用到的話)匹配。

e. 確認軌跡的差動阻抗為100 Ω。

2.檢查電路板,接上電源:

a. 如果SYNC路徑中有一個緩衝器/轉換器,確保其正常工作。

b. 確認SYNC~源和板電路(SYNC+和SYNC-,若為差分)配接是否正確,產生符合SYNC~接收元件要求的邏輯電位。如果邏輯電位不相容,應檢查電路的來源和接收配置以找出問題,否則請諮詢元件製造商。

c. 確認JESD204B串列發送器和板電路配接是否正確,產生符合JESD204B串列資料接收器要求的正確邏輯電位。如果邏輯電位不相容,應檢查電路的來源和接收配接以找出問題,否則請諮詢元件製造商。

3.檢查SYNC~信號:

a. 如果SYNC~為靜態邏輯電位,連結將停留在CGS階段。可能是所發送的資料有問題,或者JESD204B接收器未對樣本進行正確解碼。確認發送的是/K/字元,確認接收配置設置,確認SYNC~源,檢查板電路,考慮加壓SYNC~信號並強迫連結進入ILAS模式,從而找出連結RX和TX問題。否則請諮詢元件製造商。

b. 如果SYNC~為靜態邏輯高電位,確認源元件是否正確配接了SYNC~邏輯電位。檢查上箝和下箝電阻。

c. 如果SYNC~脈衝變為高電位,然後返回邏輯低電位狀態且持續時間少於六個多重框架週期,則JESD204B連結會從CGS階段前進到ILAS階段,但會停留在後一階段。這可能意味著/K/字元正確,CDR的基本功能正常。請參閱「ILAS故障排除」部分。

d. 如果SYNC~變為高電位且持續時間大於六個多重框架週期,則連結會從ILAS階段前進到資料階段,但會在後一階段發生故障;相關故障排除提示請參閱「資料階段」部分。

4.檢查串列資料

a. 確認TX資料速率與接收器的預期速率是否相同。

b. 用高阻抗探針(差動探針,如果可以用到的話)測量通道;如果字元看起來錯誤,確保通道差動軌跡匹配,PCB上的返回路徑未中斷,並且元件正確焊接到PCA上。不同於ILAS和資料階段的(看似)隨機字元,CGS字元很容易在示波器上識別(若使用速度足夠高的示波器)。

c. 用高阻抗探針驗證/K/字元。

i. 如果/K/字元正確,則連結的Tx端工作正常。

ii. 如果/K/字元不正確,則Tx元件或板通道信號有問題。

d. 若是直流耦合,確認發送器和接收器共模電壓在元件的要求範圍內。

iii. 根據所施行方案的不同,發送器共模電壓的範圍是490 mV到1135 mV。

iv. 根據所施行方案的不同,接收器共模電壓的範圍是490 mV到1300 mV。

b. e. 檢查資料通道上的發送器CML差動電壓(注:CML差動電壓等於信號各側的電壓擺幅的兩倍)。

i. 對於3.125 Gbps及以下的速度,發送器CML差動電壓的範圍是0.5 - 1.0 V pk-pk(峰對峰)。

ii. 對於6.374 Gbps及以下的速度,發送器CML差動電壓的範圍是0.4 – 0.75 V pk-pk。

iii. 對於12.5 Gbps及以下的速度,發送器CML差動電壓的範圍是0.360 – 0.770 V pk-pk。

c. f. 檢查資料通道上的接收器CML差動電壓(注:CML差動電壓等於信號各側的電壓擺幅的兩倍)。

i. 對於3.125 Gbps及以下的速度,接收器CML差動電壓的範圍是0.175 - 1.0 V pk-pk。

ii. 對於6.374 Gbps及以下的速度,接收器CML差動電壓的範圍是0.125 – 0.75 V pk-pk。

iii. 對於12.5 Gbps及以下的速度,接收器CML差動電壓的範圍是0.110 - 1.05 V pk-pk。

d. g. 如果有預先加重的選項,應啟動該選項並觀察資料路徑上的資料信號。

e. h. 確認發送器與接收器的M和L值是否一致,不然資料速率可能不匹配。例如,M=2且L=2這種情況的預期序列介面資料速率,比起M=2且L=1這種情況時將是其1/2。

f. i. 確保進入發送器和接收器的元件時脈已鎖相且頻率正確。

停留在ILAS模式:如果SYNC變為高電位且持續大約四個多重框架:

1. 連結參數衝突

a. 確認連結參數未偏移1(許多參數規定為值-1)。

b. 確認ILAS多重框架傳送正確,確認Tx元件、RX元件和ILAS第二多重框架傳送的連結參數正確。

c. 計算預期ILAS長度(tframe、tmultiframe、4xtmultiframe),確認ILAS已嘗試大約四個多重框架。

2. 確認所有通道工作正常。確保不存在多重通道/多重連結衝突。

進入資料階段但連結偶爾會重置(先返回CGS和ILAS階段,再進入資料階段):

1. 週期性或帶有間隙的週期性(Periodic or Gapped Periodic)SYSREF或SYNC~信號出現無效的設定和維持時間。

2. 連結參數衝突

3. 字元替換衝突

4. 擾碼(scrambling)問題,若啟用

5. 通道資料損壞、高雜訊或抖動可能迫使眼圖(Eye Digarm)閉合

6. 雜散時脈(spurious clocking)或元件時脈的抖動過大

關於排除連結故障的其他一般提示:

- 以允許的最低速度運行轉換器和連結,這樣就可以使用較容易獲得的低頻寬測量儀器。

- 設置允許的最少M、L、K、S組合

- 儘可能使用測試模式

- 使用Subclass 0來排除故障

- 排除故障時請關閉擾碼(scrambling)

本故障排除指南並無法包含所有可能的情況,但做為使用JESD204B的基礎,以及希望瞭解更多資訊的工程師,本文可提供一些不錯的基本知識。

以上是JESD204B規範的概述,並提供了連結相關的實用資訊。希望接觸到這一最新高性能介面標準的工程師能從中獲益,並對排除故障有所助益。

本文原篇名為:Grasp the critical issues for a functioning JESD204B interface

作者簡介

Anthony Desimone是ADI公司高速轉換器部門應用工程師。他擁有羅威爾大學(美國麻塞諸塞州)電機工程學士學位和塔夫斯大學電機工程碩士學位。

Michael Giancioppo是ADI公司高速轉換器部門應用工程師。

|

SYNC |

SYNC |

|

LANE0 |

通道0 |

|

LANE1 |

通道1 |

|

Device CLK |

元件時脈 |

|

Frame Clock |

框架時脈 |