2014年6月11日--USB 3.0能夠提供達5 Gbps的資料傳輸率,且比USB 2.0快10倍以上。這有利於滿足消費者大幅增加的、需求,以存取來接入及分享影片視訊、音樂及相片等高品質內容之需求。支援USB 3.0的晶片組已經縮減製程幾何尺寸及封裝尺寸,從而可以達到如此高的資料率,同時還配合開發更小、更低能耗能、功能豐富的可攜式媒體產品。超快資料線路及小幾何尺寸元件的結合,大幅增加了產品遭受靜電放電(ESD)影響的風險。此文專門針對USB 3.0介面審視ESD保護及阻抗匹配問題,以確保可靠、不受干擾純淨的高速資料傳輸。

為了使USB 3.0支援5 Gbps的資料率,在舊的USB 2.0資料對(D+和D-)基礎上增加了兩個差分資料對(超高速Tx及Rx)。此外,配合USB 3.0的晶片組以低至22 nm的半導體製程為基礎。USB 3.0相對於 USB 2.0傳輸的頻率升高,催生了在超高速線路上布設外部ESD保護元件時必須符合的嚴格阻抗匹配窗口。訊號線路上增添任何少量的電容,都會改變阻抗,且因此降低資料傳輸的總體訊號完整性。圖1顯示了無損耗傳輸線路的電路表徵,其中額定阻抗表徵為Z0。

Z0 = √ (L / C) = 線路阻抗

圖1:無損耗傳輸線路等效電路圖

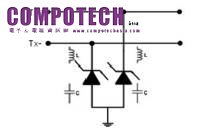

此傳輸線路模型能應用於幾乎任何當今高速串列介面中存在的資料線路中。此模型可以用於評估將ESD保護裝置元件置於一條或多條資料線路上的效應。在最基本的形式下,可以看到用以保護的資料線路的齊納二極體形式的ESD保護裝置元件。此二極體有相應的結電容,以及源自封裝內部接合線(bond wire)的少量串列電感,而此串列電感會變成資料線路的寄生組件元件,如圖2所示。由於ESD保護裝置元件中典型接合線的電感感抗通常不高於1 nH,而且ESD保護裝置元件的電容必須不高於1 pF,對於2.5 GHz USB 3.0訊號而言,圖2中電感器的阻抗將低於電容的阻抗,在討論中可以忽略此電感感抗。

圖2:ESD保護裝置元件寄生組元件模型

隨著資料線路上電壓的變化,需要少量的電流來給寄生電容充電。在高頻時,訊號線路的電壓迅速變化,此額外充電電流可能相當可觀,因而降低了資料線路中流動的電流。此電流的降低導致資料線路阻抗輕微變化,影響它傳輸的功率總額。如果功率傳輸損耗過高,資料線路訊號完整性就會出現下降。USB 3.0規格允許最大寄生電容為1.1 pF(此值包含系統中在USB控制器外部的任何電容)。ESD保護元件的電容僅占系統外部電容中的一小部份。因此,當選擇此類元件時,工程師應當始終謹記,保護元件的較低電容不僅維持資料線路的的訊號完整性,還使下行系統中能夠有更大的電容預算。

幾乎所有ESD保護元件供應商都會標示出1 MHz時的結電容。但僅有少部份供應商也會標示更高頻率時的結電容。為了極佳地表徵高速應用中的實際元件電容,應當考慮在寬廣頻率範圍量測電容。在USB 3.0中,這就等同於在2.5 GHz基礎頻率及其7.5 GHz三次諧波頻率時進行量測。就像任何電容器一樣,保護元件的電容值會隨著工作頻率之變化而變化,原因就在於寄生阻抗,稱作等效串列電容(ESR)。電容的阻抗在較低頻率低ESR條件下會保持電容性,然後阻抗持續降低,直至達到電容諧振頻率。一旦達到諧振,電容的阻抗將隨著ESR的上升而變成電感性。

保護元件反射而導致的訊號損耗是另一個重要參數——這通常表述為返回損耗的形式。返回損耗量測的是入射波從待測元件反射所出現的能量損耗有多少。ESD保護元件的返回損耗越低,看到的反射就會越少——相當於更多的訊號正在被傳輸。市場上的許多 ESD保護元件在高於5 GHz頻率時寄生電容可能會大幅升高,原因就是阻抗達到諧振並變為電感性。

對於工程師而言,理解對於資料線路阻抗通道有影響的ESD保護元件的關鍵參數至關重要。先進ESD保護元件與良好電路板布線技巧的組合,使工程師能夠從在設計中整合受保護的USB 3.0介面而受益,而無須在訊號完整性上折衷。