為提供更佳的用戶體驗,筆記型電腦及其轉接器不斷向小型化、高功率密度化方向發展,便於消費者外出時攜帶更方便,同時,還需具備高平均能效和極低待機功耗,以符合日趨嚴格的各種能效法規。如於2016年1月1日生效的歐盟CoC V5 Tier 2 規定,輸出功率為45 W和65 W的AC-DC轉接器平均能效需分別達到87.7%和89%,待機功耗分別低於75 mW和150 mW,並且還要求10%負載條件時的能效需分別達到77.7%和77.5%。電源設計工程師面臨體積、能效和成本等多方面的設計挑戰。

表1. AC-DC 轉接器能效法規一覽

切換頻率直接決定交換式電源供應器的功率密度,提高切換頻率可有效地減小無源功率元件元件如變壓器、輸出電容的尺寸,從而提高功率密度;高功率密度應用僅滿足能效規範遠遠不夠,因為體積減小時,散熱面積也相應減少,需提高能效以減少發熱,減小對內部元元件元件壽命的影響;此外,工程師需將成本控制在合理範圍內,以在競爭激烈的市場處於有利地位。

準諧振返馳 + 同步整流 = 高功率密度轉接器

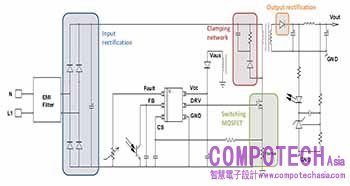

LLC拓撲結構可提供高頻率和高能效,但其成本較高,且對輸入電壓範圍有嚴格要求,不適用於筆記型電腦這一功率等級。採用準諧振返馳拓撲加上同步整流(SR)可輕鬆地設計出滿足體積、能效、成本等要求的高功率密度轉接器,如安森美半導體的高頻準諧振返馳控制器NCP1340/1+SR控制IC NCP4305/80。

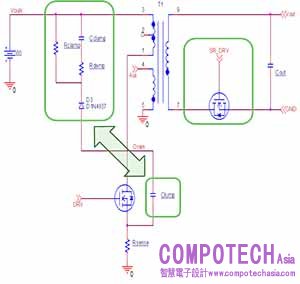

準諧振模式允許使用相對大的緩衝電容Clump,額外增加的Clump (10-22pF)可以減少MOS管關斷損耗,減少電磁干擾(EMI)。準諧振返馳有利於次極端加SR,可降低整流二極體導通損耗,減少次極端整流管尖峰電壓,降低其耐壓要求。

圖1. 準諧振模式允許使用相對大的緩衝電容Clump

準諧振式返馳電源損耗分析和設計要點

分析準諧振返馳損耗旨在提高工作頻率後再減少功率損耗。準諧振返馳電源的損耗主要分佈在初級MOSFET、尖峰吸收電路、變壓器和輸出整流。

圖2. 準諧振返馳電源的損耗分佈

1.初級MOSFET損耗分析

初級MOSFET損耗主要包括導通損耗、切換損耗和驅動損耗。導通損耗由漏源導通阻抗Rds(on)和初級端均方根電流定義。對於切換損耗,由於MOSFET的結電容與其Vds電壓成非線性比例,所以不能用簡單的電容儲能公式計算,需要將實際的結電容考慮進去,結電容可理解為MOSFET DS 網路間等效的除了MOSFET內部的結電容外的其他電容。驅動損耗在切換頻率較低時可以不作考慮,但在高頻應用中不能忽略,它在MOSFET導通和關斷時產生,主要取決於MOSFET總門極電荷Qg、切換頻率和IC工作電壓Vcc,損耗大部分消耗在驅動電阻上。

因此,對於MOSFET的選取,在高頻應用中,Rds (on) x Qg乘積數越低越有利於降低導通損耗和驅動損耗。應選擇體積小、薄且散熱性好的低熱阻封裝。由於氮化鎵(GaN) MOSFET具有更優的Rds (on) x Qg參數,可額外增加約0.3%的滿載效率,而在成本允許的情況下,GaN MOSFET是理想的選擇。

2. 尖峰吸收電路損耗分析

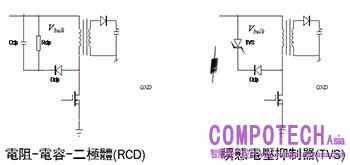

尖峰吸收電路主要用於鉗制MOS管Vds電壓,防止其過壓擊穿。電阻-電容-二極體(RCD)吸收和瞬態電壓抑制器(TVS)吸收是兩種常用的電路,其中RCD最為常用,可靠性較高。

圖3. 兩種常見的尖峰吸收電路

對於RCD電路中,較大的吸收電容C可減少鉗位電壓紋波,但會增加待機功耗,所以C的選取一般以滿載時5%至10%鉗位電壓紋波為宜。如果吸收電阻R較熱,可減小變壓器漏電感,選用Trr一致性好的慢管,可降低鉗位電壓,減少R損耗。

鉗位電壓方面,選擇高的鉗位電壓可降低RCD吸收損耗,但需選高耐壓MOS管,這會導致成本增加,而且變壓器初級電流衰減速度會變快,次級整流電流上升斜率變陡,不利於EMI和次級同步整流效率優化。選擇低的鉗位電壓,有利於EMI,次級同步整流控制,但RCD吸收損耗會增加。整流二極體D選用慢管可減少鉗位電壓和改善EMI,但二極體溫升會較高。所以需綜合考慮各方面影響,權衡擇取。

3. 變壓器損耗分析

變壓器損耗主要包括磁芯損耗、線圈損耗和高頻附加的磁芯及線圈損耗。對於>300 KHz應用,相比TP4A, 3C90或3F3,3C95/P51磁芯材料具有更低損耗。高頻應用時,臨近效應和趨膚效應導致繞線交流電阻增大,銅損增加,多股絞線將是非常不錯的選擇。

提高切換頻率,可以減少變壓器初級電感量,從而減少磁芯損耗。採用多股膠合線,減少趨膚效應,分開初級繞組(三明治繞法)以降低鄰近效應。如安森美半導體的45 W參考設計選用RM7變壓器,採用多股線加三明治繞法,初級端為24轉25x AWG#38 絞合線,次級端為4轉150x AWG#44 絞合線,採用3C90材料。

4. 輸出整流損耗分析

輸出整流通常有二極體整流和SR兩種方案。由於SR MOS導通壓降遠低於二極體導通壓降Vd,所以可比傳統的二極體整流實現更高能效。

和初級MOSFET一樣,SR損耗分為切換損耗(低壓時可忽略不計)、驅動損耗(取決於Qg、切換頻率及Vcc)和導通損耗。其中導通損耗包括MOSFET導通時的內阻損耗和體二極體在MOSFET導通前的導通損耗,體二極體導通損耗和MOSFET導通延時密切相關。安森美半導體的NCP4305/80系列同步整流控制IC具有極短導通延時,可調至30 ns,同時具有強大的驅動能力,能快速通斷SR MOSFET。如在45 W參考設計中,SR MOSFET選用NVMFS6B03NL,內阻僅4 mΩ,Qg 70.7nC,若選用GaN SR MOSFET將可獲得額外約0.3%的滿載能效提升。

綜上所述,損耗源及影響損耗的因素可歸納為:

表2. 損耗源及影響損耗的因素

45 W高功率密度轉接器參考設計

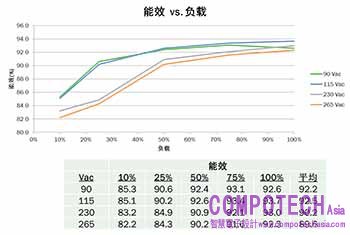

該參考設計採用安森美半導體的NCP1340高頻準諧振返馳+NCP43080 SR架構, 在能效和待機功耗方面彰顯出色性能,提供19 V/2.4 A額定輸出,90-264 V寬輸入電壓,體積僅50 mm x 33 mm x 22 mm,所需週邊元件數少,滿載能效超過92%,待機功耗低於30 mW,完全符合CoC V5 Tier 2能效要求。

圖4. 45 W參考設計能效 vs. 負載曲線

其中NCP1340/1採用SO-8封裝,高壓啟動,集成X2放電和欠壓檢測,運行達6個穀底鎖定切換,可有效地解決因穀底數不穩定所產生的音頻雜訊問題,並通過最小頻率鉗位和Quiet-Skip運行消除雜訊。人類能聽到的頻率範圍是20Hz至20kHz,早期的跳週期控制IC將最低切換頻率設置在25 kHz,但間隙工作頻率通常會在2 kHz至4 kHz範圍,所以一旦其進入跳週期模式,雜訊還是很大的。Quiet-Skip將最大的間隙工作頻率設置為800 Hz,雖然800 Hz仍在可聽見的範圍內,但其往往會與背景雜訊很好的融合,所以不容易被察覺。NCP1340/1採用跳週期模式,電流消耗低,因而可實現低於30 mW的低待機功耗,具有頻率抖動特性,可提升EMI性能,實測抖頻功能可降低AV曲線低頻段的峰值約5 dB。此外,NCP1341比NCP1340多了功率倍增模式,可提高瞬態帶載能力,同時保持最小尺寸的變壓器,實現1.5倍或2倍的額定功率輸出,非常適合印表機、驅動電源等需要損失功率倍增的應用場合。

總結

設計高功率密度的轉接器電源不但要滿足更輕更薄的發展趨勢以提升用戶體驗,還要符合日趨嚴格的能效要求,這對設計人員來說充滿挑戰。高頻準諧振返馳是適用於低於65 W的高功率密度電源轉接器的拓撲結構之一。安森美半導體的45 W高功率密度參考設計採用準諧振返馳NCP1340/1 + 同步整流NCP4305/80的架構,可輕鬆設計出小巧、低成本的高能效高功率密度轉接器,滿載能效超過92%,待機功耗低於30 mW,遠遠超越能效規範。