ADI 精密資料擷取訊號鏈的雜訊分析

前言:

ADI儀器儀錶、航空航太與防務業務部應用工程師 Maithil Pachchigar

簡介

在很多應用中,類比前端接收單端或差分訊號,並執行所需的增益或衰減、抗混疊濾波及位準轉換,之後在全刻度位準下驅動ADC輸入端。本文將探討精密資料擷取訊號鏈的雜訊分析,並深入研究此種訊號鏈的總雜訊貢獻。

在很多應用中,類比前端接收單端或差分訊號,並執行所需的增益或衰減、抗混疊濾波及位準轉換,之後在全刻度位準下驅動ADC輸入端。本文將探討精密資料擷取訊號鏈的雜訊分析,並深入研究此種訊號鏈的總雜訊貢獻。

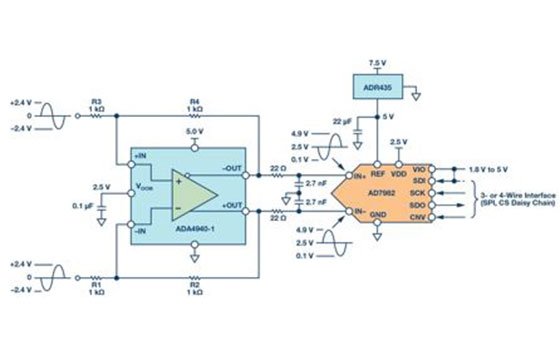

如圖1所示,低功耗、低雜訊、全差分放大器ADA4940-1驅動差分輸入、18位元、1 MSPS PulSAR® ADC AD7982,同時低雜訊精密5 V基準電壓源ADR435用來提供ADC所需的5 V電源。此訊號鏈無需額外驅動器級和基準電壓緩衝器,因此簡化了類比訊號調理,可節省電路板空間和成本。將一個單極點截止頻率2.7 MHz RC(22 Ω,2.7 nF)低通濾波器放在ADC驅動器輸出和ADC輸入之間,有助於限制ADC輸入端雜訊,並減少來自逐次逼近型(SAR) ADC輸入端容性DAC的反沖。

圖1.低功耗全差分18位元1 MSPS資料擷取訊號鏈(簡化示意圖:未顯示所有連接和去耦)。

ADA4940-1用作ADC驅動器時,使用者可以進行必要的訊號處理,包括對訊號實施位準轉換和衰減或放大,以便使用四個電阻實現更大動態範圍,從而不再需要額外的驅動器級。採用回饋電阻(R2 = R4)對增益電阻(R1 = R3)之比設置增益,其中R1 = R2 = R3 = R4 = 1 kΩ。

對於平衡差分輸入訊號,等效輸入阻抗為2×增益電阻(R1或R3) = 2 kΩ,對於非平衡(單端)輸入訊號,等效阻抗根據下式計算,約為1.33 kΩ

如果需要可以在輸入端並聯一個終端電阻。

ADA4940-1內部共模回饋迴路強制共模輸出電壓等於施加到VOCM輸入的電壓,同時提供良好的輸出平衡。當兩個回饋係數(β1和β2)不相等時,差分輸出電壓取決於VOCM;此時,輸出幅度或相位的任何不平衡都會在輸出端產生不良共模成分,導致差分輸出中有冗餘雜訊和失調。因此,在這種情況下(即,β1 = β2),輸入源阻抗和R1 (R3)的組合應等於1 kΩ,以避免各輸出訊號的共模電壓失配,並防止ADA4940-1的共模雜訊增加。

訊號在印刷電路板(PCB)的走線以及長電纜中傳輸時,系統雜訊會疊加到訊號中,差分輸入ADC會抑制訊號雜訊,並表現為一個共模電壓。

該款18位元1 MSPS資料擷取系統的預期訊號雜訊比(SNR)理論值可透過每個噪音源(ADA4940-1、ADR435和AD7982)的和方根(RSS)計算得出。

ADA4940-1在100 kHz時的低雜訊性能典型值為3.9 nV/√Hz,如圖2所示。

圖2.ADA4940輸入電壓雜訊頻譜密度和頻率的關係。

必須計算差分放大器的雜訊增益,以便找到等效輸出雜訊貢獻。

差分放大器的雜訊增益為:

其中

以及

是兩個回饋係數。

應當考慮下列差分放大器雜訊源

由於ADA4940-1輸入電壓雜訊為3.9 nV/√Hz,其差分輸出雜訊應當為7.8 nV/√Hz。ADA4940-1產品手冊中的共模輸入電壓雜訊(eOCM)為83 nV/√Hz,因此其輸出雜訊為:

給定頻寬條件下,R1、R2、R3和R4電阻雜訊可根據詹森-奈奎斯特雜訊方程計算出:

由於ADA4940-1輸入電壓雜訊為3.9 nV/√Hz,其差分輸出雜訊應當為7.8 nV/√Hz。ADA4940-1產品手冊中的共模輸入電壓雜訊(eOCM)為83 nV/√Hz,因此其輸出雜訊為:

給定頻寬條件下,R1、R2、R3和R4電阻雜訊可根據詹森-奈奎斯特雜訊方程計算出:

其中kB是玻爾茲曼常數(1.38065 × 10 – 23 J/K),T為電阻絕對溫度(開爾文),而R為電阻值(Ω)。

來自回饋電阻的雜訊為:

來自回饋電阻的雜訊為:

來自R1的雜訊為:

來自R3的雜訊為:

ADA4940-1產品手冊中的電流雜訊為0.81 pA/√Hz。

反相輸入電壓雜訊:

ADA4940-1產品手冊中的電流雜訊為0.81 pA/√Hz。

反相輸入電壓雜訊:

同相輸入電壓雜訊:

因此,來自ADA4940的等效輸出雜訊貢獻為:

(RC濾波器之後)的ADC輸入端總積分雜訊為:

AD7982的均方根雜訊可根據5 V基準電壓源情況下的典型訊號雜訊比(SNR,98 dB)計算得出。

根據這些資料,ADC驅動器和ADC的總雜訊貢獻為

注意,本例中忽略來自ADR435基準電壓源的雜訊貢獻,因為它非常小。

因此,資料擷取系統的理論SNR可根據下式近似計算。

圖3.FFT曲線圖,fIN = 1 kHz,FS = 1 MSPS (將ADA4940-1配置成全差分驅動器)。

AD7982在1 kHz輸入訊號時,SNR典型值為96.67 dB,THD典型值為-111.03 dB,如圖3中的FFT性能所示。這種情況下測得的SNR為96.67 dB,非常接近上文中的96.95 dB SNR理論估算值。產品手冊中98 dB的目標SNR的實際損耗由來自ADA4940-1差分放大器電路的等效輸出雜訊貢獻所導致。

針對給定應用選擇ADC驅動器以驅動SAR ADC時,雜訊是一個重要規格,詳細查閱頻寬、建立時間、輸入和輸出上裕量/下裕量以及功耗要求也很重要。有關驅動高解析度精密PulSAR ADC的推薦放大器的更多資訊,請參閱ADI 公司ADC驅動器選型指南。相關設計差分放大器電路資訊,請下載免費且直覺易用的ADI公司DiffAmpCalc™工具。