高性能電壓監控器詳解—第一部分

前言:

作者:ADI 產品應用工程師Noel Tenorio 和 Anthony Serquiña

摘要

本文闡述了高性能電壓監控器的價值,討論其基本定義、工作原理、技術規格、拓撲結構和極性。文中提到的高性能電壓監控器目的在協助基於微處理器的系統提升可靠性,防止掉電狀況下系統出錯,並提供一些示例作為參考。

引言

諸如嵌入式系統等需要進行大量運算和資料處理的應用,通常會使用微控制器、微處理器和現場可編程閘陣列(FPGA)等元件來執行複雜的運算常式,因為這些元件具有多功能性、高速度和彈性。然而,這些推薦使用的元件也存在限制和不同的電源要求,如果在系統開發的早期階段未納入考量,系統的性能和可靠性可能會受影響。其中一個限制是當出現掉電狀況時,系統可能會出現故障,當電源電壓降至最低工作電壓以下時,微控制器可能會發生故障並導致系統出錯。幸運的是,電壓監控器便是專門設計來解決這個問題。

本文所討論的高性能電壓監控器包括ADI的產品系列,並介紹電壓監控器的功能、輸入和輸出基礎以及高性能電源監控產品的其他基礎知識。

電壓監控器定義及其工作原理

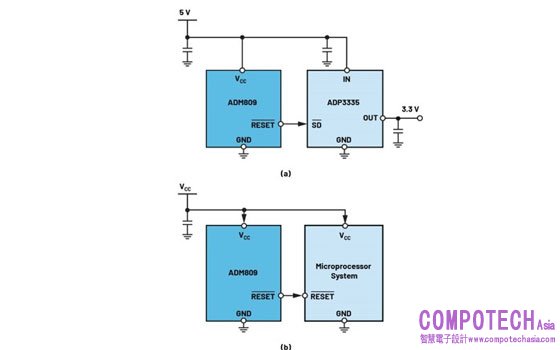

電壓監控器是一類用於監控電壓供應軌的元件,只要滿足監控條件,其就會提供一個可用來執行某種操作的輸出,並檢測被監控電壓供應軌是否低於或超過預定義的電壓水準(稱為閾值)。1 其提供的輸出訊號通常稱為重設訊號,用於將另一個元件置於另一種工作模式,例如重設模式或活動模式。對於那些在特定電壓範圍之外運行會導致錯誤和故障的應用來說,使用電壓監控器也是十分適用的。有時,復位輸出也用於致能和禁用另一個元件,例如在任何需要一定輸入電壓範圍才能正常運行的應用中。一個典型的應用例子,是使用電壓監控器來讓穩壓器正常運行,如圖1a所示。為了確保啟動期間正常運行,LDO穩壓器要求輸入中有足夠的能量,或者說需要夠高的輸入電壓水準。2

眾所皆知,電壓監控器是與微控制器或MCU密切相關的搭檔。當正在執行指令時,如果電源電壓降至最低工作範圍以下,MCU就有發生故障和造成系統出錯的風險。在此種情況下,MCU的電源電壓即為被監控電壓,MCU的最低工作電壓應為閾值電壓。我們將在文中進一步討論如何定義閾值位準。用於監控微控制器電源的電壓監控器的一個簡單例子是ADM809如圖1b所示。監控器感測被監控的電壓水準,並將其送入 VCC 接腳。一旦被監控的電壓低於閾值,低位準有效重定輸出就會將微處理器置於重定模式,直至電壓供應恢復到正常水準。3

圖1. ADM809是電壓監控器的一個簡單例子,其監控輸入電壓以(a)在輸入電壓水準處於正確範圍以內時使能LDO穩壓器,並(b)在掉電狀況下將微處理器系統置於重設模式。

電壓監控器有哪些重要輸入規格參數?

要進一步了解電壓監控器,就需要先瞭解四個重要輸入規格參數。這將有助於系統設計人員建置電壓監控器來提升系統在應用中的可靠性。這些規格參數包括重定閾值、閾值精度、復位閾值滯回和上電復位。

復位閾值

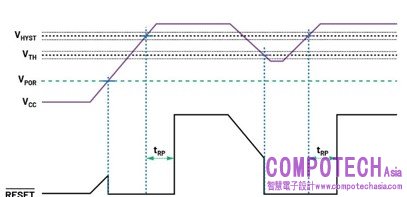

重設閾值是電壓位準;當被監控的電壓低於此值時,就會發出重設訊號。在電壓監控器產品中,重設閾值通常標記為 VTH。當被監控電壓 VCC降至重設閾值電壓 VTH以下時,其會產生低位準復位輸出,如圖2中的時序圖所示。在應用中,閾值電壓設定為允許系統正常運行的最小電壓。

圖2. 電壓監控器的被監控電壓 VCC和重定輸出訊號的時序圖。

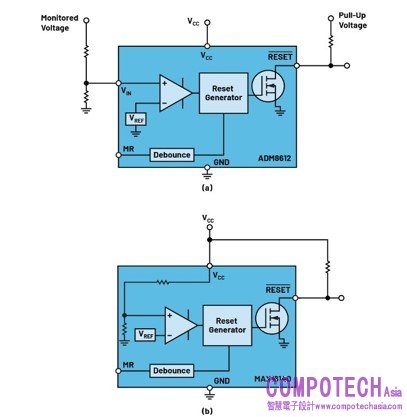

設定復位閾值的一種方法是透過外部電阻分壓器。被監控電壓的一小部分透過與基準電壓源進行比較,以瞭解被監控電壓是否高於或低於復位閾值,如圖3a所示。ADM8612 是此配置的一個例子。一些電壓監控器的重定閾值是在工廠透過鐳射調整由內部電阻分壓器設定的,例如 MAX16140。這帶來了一些優勢,例如外部元件更少,可以為解決方案騰出額外空間,滿足精巧型應用的需求,如圖3b所示。它還能實現更高的精度,因為其不依賴於外部因素(例如使用具有容差的標準值電阻)。然而,外部電阻方案可支援彈性調整復位閾值位準。

圖3. 復位閾值的設定方法:(a) ADM8612復位閾值透過外部電阻分壓器設 定,(b) MAX16140復位閾值透過工廠調整的內部電阻分壓器設定。

閾值精度

閾值精度是指實際閾值與計算的重定閾值或目標重定閾值的接近程度。一些因素會影響閾值的精度,包括電阻分壓器和基準電壓。電阻分壓器和基準電壓都是類比電路,會受到溫度等環境因素的影響,導致復位閾值具有一定的容差。基準電壓和電阻越穩健,容差就越嚴格,閾值精度就越高。閾值精度通常以百分比表示。假設電壓監控器的閾值精度為±1%,閾值設定為3.3 V,那麼實際閾值可能在3.267 V至3.333 V左右。

瞭解閾值精度非常重要,因為這對於設定復位閾值十分重要。如果在設定復位閾值時不考慮精度,系統可能會陷入不理想的故障區域。

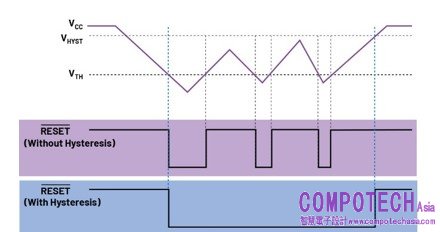

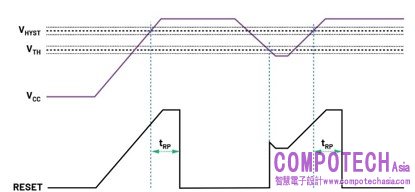

復位閾值滯回

重定閾值滯回是指被監控的電壓回到正常區域後,取消重設訊號所需的額外電壓。在監控欠壓的電壓監控器中,重設閾值滯回通常表示為 VHYST 或 VTH+HYS。滯回有多項益處。首先,其確保被監控的電壓回到正常水準,並且相對於閾值有一定的安全餘裕。其次,它能讓電源在復位取消之前先穩定下來,進而有助於解決電源雜訊和不穩定性問題。在沒有滯回的情況下,當被監控電壓超過閾值時,電壓監控器會反覆發出或取消重設訊號。4,5 這可能發生在具有電源雜訊的應用中,或發生在電池供電的系統中,因為受內部電阻的影響,電壓會隨著負載電流而下降。圖4中的紫色陰影區域顯示了一個例子。同時,由於存在滯回,重設輸出將使系統保持重設模式,直到電源穩定為止,進而可消除系統的不穩定和振盪行為,如圖4.4中的藍色陰影區域所示。

圖4. 有滯回和無滯回的復位輸出行為比較。

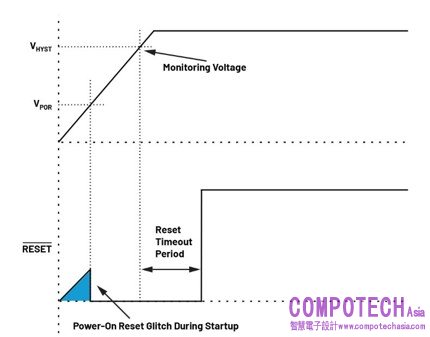

上電復位

在啟動期間,當電源電壓開始上升時,電壓監控器的內部電路沒有足夠的偏置。因此,重設輸出處於未定義狀態。隨著電源電壓繼續上升,其將達到某一電壓供應水準,使電壓監控器脫離未定義狀態並發出有效的重設訊號。讓監控器處於規定狀態並提供有效重定輸出的最小電源電壓稱為上電重定電壓或 VPOR。 考慮圖3b中的電壓監控器簡化示意圖。假設開漏復位輸出上拉至 VCC,在未定義狀態下,重定輸出將反映電源電壓 VCC。這會在復位輸出中產生一個突刺,稱為上電突刺。6 當電源電壓達到 VPOR時,監控器就會發出有效的重設輸出訊號,如圖5所示。

圖5. 啟動過程中的上電突刺和上電重定電壓 VPOR。

在某些應用中,上電突刺會被忽略且無關緊要,例如在高壓系統中。但是,對於某些應用來說(例如在邏輯高電壓閾值較低的元件中) 這是不可取的。7

電壓監控器有哪些輸出規格參數需要考慮?

設計電壓監控器時,需要考慮的一個因素是復位輸出極性和時序。您可以根據應用選擇極性——低位準有效輸出或是高位準有效輸出。

低位準有效

低位準有效輸出表示只要被監控電壓低於閾值電壓,重設輸出就會變為低位準。圖2中的時序圖顯示了具有低位準有效輸出的電壓監控器的回應。為了便於識別,低位準有效重設輸出標記為RESET (讀作RESET bar)。當被監控電壓上升到閾值電壓以上時,RESET輸出將在指定時間內保持有效,然後才會變為高位準。此時間延遲稱為復位超時週期 (tRP),其可以是固定時間,也可以透過外部電容調整。

高位準有效

根據輸出要求,系統可能需要高位準有效輸出。與低位準有效輸出相反,在高位準有效輸出中,當被監控電壓低於閾值時,復位輸出變為高位準;當被監控電壓在重定超時週期 tRP後上升到閾值電壓以上時,重定輸出變為低位準。圖解參見圖6。

圖6. 高位準有效重定輸出的VCC和重定訊號的時序圖。

根據具體應用,需要考慮的另一個因素是輸出拓撲結構。主要使用兩種輸出拓撲結構——開漏拓撲和推挽拓撲。

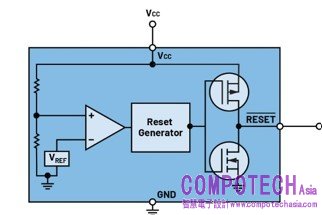

推挽輸出拓撲

推挽輸出拓撲由一對互補MOSFET組成,如圖7所示。當底部FET關斷且頂部FET導通時,復位輸出變為高位準;當底部FET導通且頂部FET關斷時,復位輸出變為低位準。推挽輸出提供從低位準到高位準、從高位準到低位準的幾乎軌對軌的高速回應。

圖7. 推挽輸出拓撲。

低位準有效推挽復位輸出適用於大多數應用,但也可採用其他輸出類型。如圖8所示,單電壓系統中的推挽輸出很簡單,但多電壓系統中的推挽輸出需要更加留心,尤其是當微控制器只有一個復位輸入時。8

圖8. 單電壓系統。

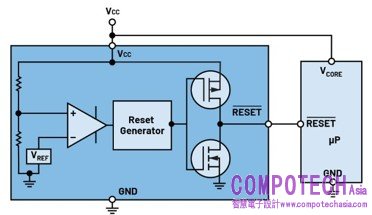

開漏輸出拓撲

對於開漏拓撲,監控電路的重定輸出是內部MOSFET的漏極。為了產生類似圖3b所示的邏輯訊號輸出,需要從重設連接一個外部上拉電阻到電源電壓。當MOSFET導通時,重設訊號變為低位準;當MOSFET關斷時,重設訊號變為高位準。上拉電阻可以連接到除監控電路電源之外的電壓軌。這對於需要不同於監控器電源電壓的重設位準的系統來說非常有利。8

開漏輸出的另一個優點是“wired-OR”功能。將兩個或多個監控電路的開漏輸出連接到同一匯流排上,可以實現「負邏輯或」電路。9這表示當任何一個監控電路的重定輸出變為低位準時,匯流排為低位準。僅當所有重設輸出都是高位準時,匯流排才為高位準。如果想要監控多個電源,並在任何一個電源電壓下降時觸發重設,這種拓撲會很方便。

應用案例

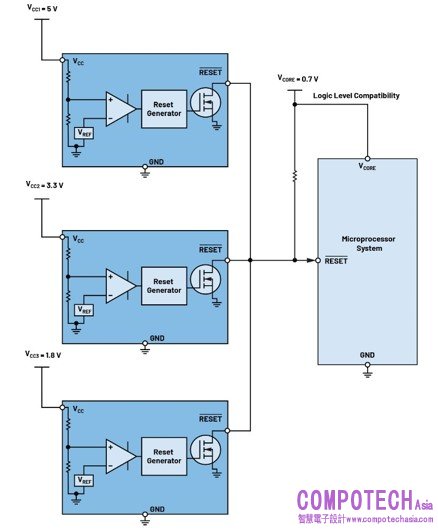

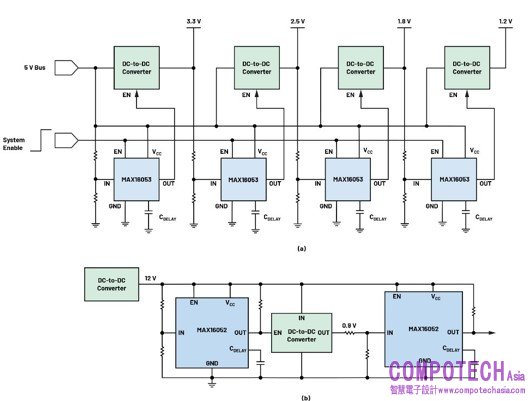

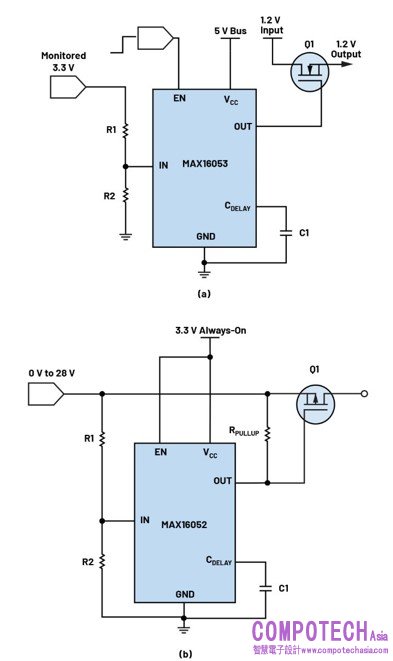

圖9、10和11顯示了電壓監控器不同輸出拓撲和極性的一些典型應用案例。圖9顯示了一個應用開漏拓撲的多電壓系統示例。在多電壓軌系統中,可以利用菊鍊連接的低位準有效輸出來執行時序控制,如圖10a和10b所示。在某些應用中,正確的電源時序控制可能是首要的考慮因素之一。多軌系統(如基於FPGA的解決方案)通常需要並指定適當的電源時序,以防止出現系統故障和不穩定情況。圖11a和11b顯示了應用高位準有效輸出的示例。對於這些情況,高位準有效輸出用於致能或禁用高側MOSFET,以實現開/關控制方案。此類配置可用於過壓保護、低壓時序控制等電路。高側MOSFET也可使用電壓監控器的低位準有效輸出來驅動。有關詳細資訊,請參閱文章「利用低位準有效輸出驅動高側MOSFET輸入開關以實現系統功率迴圈。」

圖9. 多電壓系統共用一個微處理器重定輸入。

圖10. 使用低位準有效輸出(a)推挽拓撲和(b)開漏拓撲的多軌時序控制

圖11. 高位準有效輸出極性的應用。(a)採用推挽拓撲的N通道MOSFET低壓時序控制。(b)採用開漏拓撲的P通道MOSFET過壓保護電路。

結論

電壓監控器用於致能、禁用或復位另一個元件,而其常見應用在於復位微控制器。監控器保護系統免受錯誤和故障的影響,進而提升應用的整體可靠性。設計時需要考慮電壓監控器的輸入、輸出和時序規格。根據監控器不同的輸出拓撲和極性,在不同的應用場景中可以發揮不同的優勢,進而實現預期功能並提高系統可靠性。

參考電路

1 「使用微處理器監控器的原因、內容、方式和時間。」ADI,2018年4月。

2 「無突刺電壓監控器基礎知識。」 ADI,2021年11月。

3 「3接腳SC70和SOT-23封裝的微處理器監控電路。」ADI,2014年10月。

4 Noel Tenorio。「電壓監控器如何解決電源雜訊和突刺問題。」《類比對話》,第57卷第4期,2023年11月。

5 Pinkesh Sachdev。「提高滯回,實現平穩的欠壓和過壓閉鎖。」《類比對話》,第55卷第1期,2021年3月。

6 「無突刺電源監控器如何促進高可靠性應用。」ADI,2021年9月。

7 Niño Angelo Pesigan、Ron Rogelio Peralta和Noel Tenorio。「利用低位準有效輸出驅動高側MOSFET輸入開關以實現系統功率迴圈。」《類比對話》,第58卷第1期,2024年2月。

8 「選擇電源監控器輸出。」ADI,2002年5月。

9 「多電壓系統的電源監控器。」 ADI,2003年11月。

10 「高壓可調時序/監控電路。」ADI,2018年。